### Masterarbeit

### FailPanda: Fehlerinjektionsexperimente auf

Lars Rademacher 19. Dezember 2013

einer eingebetteten ARM-Plattform

Gutachter:

Dipl.-Inf. Horst Schirmeier Prof. Dr.-Ing. Olaf Spinczyk

Technische Universität Dortmund Fakultät für Informatik Lehrstuhl Informatik 12 Arbeitsgruppe Eingebettete Systemsoftware http://ess.cs.tu-dortmund.de/

Hiermit versichere ich, dass ich die vorliegende Arbeit selbstständig verfasst, keine anderen als die angegebenen Quellen und Hilfsmittel verwendet sowie Zitate kenntlich gemacht habe.

Dortmund, den 19. Dezember 2013

Lars Rademacher

#### Zusammenfassung

Fehlerinjektion (FI) ist ein experimentelles Werkzeug zur Untersuchung der Zuverlässigkeit von unter Gesichtspunkten der Fehlertoleranz entwickelten Hard- und Softwaresystemen bei Fehlerpräsenz. Das FI-Framework Fail\*, welches im Rahmen des Forschungsprojekts "Dependability Aspects in Configurable Embedded Operating Systems" (DanceOS) entwickelt wird, bietet die Möglichkeit zur parallelen und verteilten Durchführung von FI-Experimenten. Die Architektur des Frameworks sieht die Verwendung von Hardwaresimulatoren als Zielsysteme vor, wobei durch eine generische Zielsystemschnittstelle ebenfalls die Möglichkeit zur Anbindung von Hardwaresystemen besteht.

Ein zentrales Problem bei der Verwendung von Simulatoren ist die eingeschränkte Aussagekraft der gewonnenen Ergebnisse aufgrund der unvermeidbaren Abweichungen vom Verhalten realer Systeme. Es ist daher zu erwarten, dass sich durch die Wiederholung einer Teilmenge der simulativ durchgeführten FI-Experimente auf realer Hardware die Aussagekraft des Gesamtergebnisses steigern lässt. In dieser Masterarbeit werden mögliche Ansätze zur FI auf einer eingebetteten ARM-Plattform (*PandaBoard ES*) auf ihre Eignung für den Einsatz mit *Fail\** untersucht und experimentell bewertet. Der Schwerpunkt der Untersuchungen liegt hierbei auf der Verwendung von Debugschnittstellen und der Bewältigung von gegebenen Einschränkungen bezüglich Durchführungsgeschwindigkeit und Hardwarezugriff. Die Bewertung von Effizienz und Aussagekraft erfolgt auf Grundlage von FI-Kampagnen und Microbenchmarks.

# Inhaltsverzeichnis

| 1 | Einf | ührung  | g und Motivation                        | 1                                                                       |

|---|------|---------|-----------------------------------------|-------------------------------------------------------------------------|

| 2 | Gru  | ndlagei | n                                       | 5                                                                       |

|   | 2.1  | •       | begriffe der Fehlerinjektion            | 5                                                                       |

|   | 2.2  |         | modelle                                 | 9                                                                       |

|   | 2.3  |         | ässigkeitsmetriken                      | 10                                                                      |

|   | 2.4  |         | injektionsverfahren                     | 11                                                                      |

|   |      | 2.4.1   | Hardware-basiert                        | 13                                                                      |

|   |      | 2.4.2   | Software-basiert                        | 14                                                                      |

|   |      | 2.4.3   | Simulator-basiert                       | 14                                                                      |

|   |      | 2.4.4   | OCD-basiert                             | 15                                                                      |

|   | 2.5  | Optim   | ierung von Fehlerinjektionsexperimenten | 16                                                                      |

|   | 2.6  | Das Fe  | ehlerinjektions-Framework Fail*         | 18                                                                      |

|   |      | 2.6.1   | Backend-Abstraktion                     | 19                                                                      |

|   |      | 2.6.2   | Kampagnenverwaltung                     | 23                                                                      |

|   | 2.7  | Zusam   | menfassung                              | 26                                                                      |

|   |      |         |                                         |                                                                         |

| 3 | Ana  | -       | nd Entwurf                              | 5<br>5<br>9<br>10<br>11<br>13<br>14<br>14<br>15<br>16<br>18<br>19<br>23 |

|   | 3.1  |         | derungsanalyse                          |                                                                         |

|   |      | 3.1.1   | Zielplattform                           |                                                                         |

|   |      | 3.1.2   | Systemarchitektur                       |                                                                         |

|   | 3.2  |         | ntentwurf                               |                                                                         |

|   |      | 3.2.1   | Pandaboard ES                           |                                                                         |

|   |      | 3.2.2   | Flyswatter 2 und OpenOCD                |                                                                         |

|   | 3.3  |         | Aufzeichnung                            |                                                                         |

|   | 3.4  |         | isierung                                |                                                                         |

|   | 3.5  |         | Navigation                              |                                                                         |

|   |      | 3.5.1   | Stand der Kunst                         |                                                                         |

|   |      | 3.5.2   | Smart-Hopping                           |                                                                         |

|   |      | 3.5.3   | Checkpointing                           |                                                                         |

|   |      | 3.5.4   | Äquivalenzklassengewahre Navigation     |                                                                         |

|   | 3.6  |         | injektion                               |                                                                         |

|   | 3.7  |         | ntersuchung                             |                                                                         |

|   | 3.8  | Zusam   | nmenfassung                             | 56                                                                      |

Inhaltsverzeichnis 0.0

| 4   | Rea   | lisierung                      | 57 |

|-----|-------|--------------------------------|----|

|     | 4.1   | Modifikation der Zielplattform | 57 |

|     | 4.2   | Anbindung von OpenOCD          |    |

|     | 4.3   | Integration in Fail*           | 63 |

|     | 4.4   | Zusammenfassung                | 66 |

| 5   | Eva   | luation                        | 67 |

|     | 5.1   | Performanz                     | 67 |

|     |       | 5.1.1 Schnittstelle            | 68 |

|     |       | 5.1.2 Trace-Navigation         | 70 |

|     |       | 5.1.3 MMU-Speicherüberwachung  | 78 |

|     |       | 5.1.4 Gesamtsystem             | 80 |

|     | 5.2   | Experimentergebnisse           | 83 |

|     | 5.3   | Zusammenfassung                | 86 |

| 6   | Erge  | ebnisse und Ausblick           | 87 |

|     | 6.1   | Ergebnisse                     | 87 |

|     | 6.2   | Ausblick                       | 88 |

| Lit | terat | urverzeichnis                  | 91 |

| Αŀ  | bildı | ungsverzeichnis                | 97 |

| Ta  | belle | enverzeichnis                  | 99 |

## 1 Einführung und Motivation

Dem Bereich mobiler hochperformanter eingebetteter Computersysteme im Markt der Verbraucherelektronik steht ein Wandel bevor. In diesem Bereich ist eine Entwicklung mit den Optimierungskriterien Performanz, Energieeffizienz und Preis für den Endverbraucher zu erkennen. In den kommenden Jahren wird die konsequente Erhöhung der Strukturdichte zur Steigerung der Performanz sowie die Reduzierung der Versorgungsspannung zur Reduktion des Energieverbrauchs ein erhöhtes Aufkommen an Hardware-Fehlern – beispielsweise Invertierungen von Speicherbits durch Strahlungseinfall – in angesprochenen Systemen hervorrufen [Bor05, DYDS+10, NX06]. Üblicherweise wird einem solchen Aufkommen von Hardware-Fehlern mithilfe von Hardware-Fehlertoleranz begegnet – beispielsweise mittels Speicher mit eingebauter ECC-Einheit. Aufgrund des hohen Preisdrucks im Bereich der Verbraucherelektronik und des verursachten zusätzlichen Energieverbrauchs [GBT04] widerspricht der Einsatz fehlertoleranter Hardware allerdings teilweise den oben genannten Optimierungszielen.

Ein alternativer Ansatz liegt in der Software-Fehlertoleranz. Hierbei werden Systemanteile durch die Einfügung zusätzlichen Codes abgesichert. Beispielsweise kann das Verfahren der Triple Modular Redundancy (kurz: TMR) betrachtet werden, welches eine abzusichernde Funktion dreifach ausführt und anschließend das Ergebnis durch einen Mehrheitsentscheid der drei Einzelergebnisse bestimmt [KK07]. Somit kann ein Fehler in einer der drei Ausführungen auftreten, ohne weitere Auswirkungen auf das Funktionsergebnis zu haben. Es ist ebenfalls möglich, Software-Fehlertoleranz gezielt auf bestimmte Variablen anzuwenden, indem etwa bei jedem Zugriff auf die Variable eine Kontrolle einer Prüfsumme durchgeführt wird [BSS13a]. Der Einsatz dieser Verfahren erfordert keine zusätzlichen Hardware-Komponenten und kann zielgerichtet an den Systemanteilen wirken, deren Absicherung zwingend erforderlich ist, wobei an den restlichen Anteilen kein oder ein schwächeres Toleranzverfahren genutzt wird. Durch diese hohe Konfigurierbarkeit können der durch Fehlertoleranz verursachte Mehraufwand und somit Performanzund Energieeffizienz-Einbußen minimiert werden.

Im Folgenden wird beispielhaft ein mobiles Video-Abspielgerät mit Einsatz von Software-Fehlertoleranz betrachtet [HESM10]. Hierbei können Hardware-Fehler auftreten, die einen Systemabsturz oder eine verfälschte Darstellung der Bildinformation des Videos verursachen können. Durch die hohe Konfigurierbarkeit von Software-Fehlertoleranz ist es möglich, nur die Systemanteile abzusichern, bei denen das fehlerhafte Verhalten für den Nutzer sichtbar wird. So werden Komponenten abgesichert, in denen auftretende Fehler zu einem Absturz führen können und Anteile des Bildspeichers, deren fehlerhafte Darstellung erkennbar ist. Eine große Menge an auftretenden Fehlern kann hingegen toleriert werden, da beispielsweise leichte Farbänderungen im Bild für den Nutzer nicht erkennbar sind. Weil die abzusichernden Komponenten im Regelfall einen kleinen An-

teil am gesamten Systemzustand ausmachen, wird hierdurch ein geringer Mehraufwand erzeugt.

Software-Fehlertoleranz entwickelt sich aufgrund seiner Vorteile auch zu einem angesehenen Verfahren in Bereichen, in denen Aufgrund hoher Anforderungen an die Ausfallsicherheit bislang ausschließlich Hardware-Fehlertoleranz eingesetzt wurde. Beispielhaft ist das Projekt des NASA SpaceCube zu nennen [WZF13]. Hier wird kommerziell erhältliche Hardware außerhalb der Erdatmosphäre verwendet, um hohe Rechenperformanz nutzen zu können. Alternative Plattformen, die Hardware-Fehlertoleranz für den Einsatz in dieser Domäne bieten, sind im Regelfall aufgrund langer Entwicklungszyklen weniger aktuell, weshalb ihre Berechnungsleistung deutlich reduziert ist. Da die starke Strahlung im Einsatzszenario des Space-Cubes ein erhöhtes Fehleraufkommen produziert und eine Wartung der Hardware sehr schwierig ist, erfolgt eine entsprechende Absicherung mittels Software-Fehlertoleranz.

Zur Bemessung der Wirksamkeit von auf ein System angewandten Software-Fehlertoleranzverfahren und zur Identifikation von Systemanteilen, deren Absicherung nötig ist, ist der Einsatz von entsprechenden Messwerkzeugen erforderlich. Ein mögliches Messverfahren ist die sogenannte Fehlerinjektion. Hierbei werden systematisch Fehler in ein zu untersuchendes System injiziert und die Auswirkungen der Injektion auf das anschließende Systemverhalten untersucht. Auf Basis dieser Untersuchungen sind statistische Aussagen über die Zuverlässigkeit des Systems möglich. Des Weiteren kann bei genauer Untersuchung der Auswirkungen von Fehlern in verschiedenen Systemanteilen eine spezifische Konfiguration von Software-Fehlertoleranzverfahren entworfen werden. Eine mögliche Realisierung des Verfahrens liegt in der Injektion von Fehlern in Hardware-Simulatoren, wodurch eine günstige Parallelisierung von Injektionsexperimenten und ein leichter Zugriff auf die simulierten Komponenten möglich ist. Im Gegensatz dazu hat eine Injektion in ein echtes Hardwaresystem den Vorteil, dass die Ergebnisse realitätsgetreuer als bei der Verwendung von Simulatoren sind [BGOS12]. Fehlerinjektion in Hardware ist schlecht parallelisierbar, da für jede zusätzliche Instanz des zu untersuchenden Systems zusätzliche Hardware vorhanden sein muss. Dieser Nachteil kann allerdings durch die im Gegensatz zum Simulator im Regelfall deutlich höhere Ausführungsgeschwindigkeit kompensiert werden.

Die Injektion in Hardwaresysteme kann beispielsweise mittels sogenannter On-Chip Debugger (kurz: OCD) erfolgen [FGAF06]. Hierbei handelt es sich um in Prozessoren integrierte Hardwarebausteine, die eine Untersuchung des Systemzustands erlauben, um beispielsweise Programmfehler zu erkennen. Zu diesem Zweck wird das Anhalten der Ausführung des Prozessors mithilfe konfigurierbarer Haltebedingungen – sogenannte Breakpoints und Watchpoints – ermöglicht und es kann der aktuelle Zustand des Systems untersucht und modifiziert werden. Konkret besteht üblicherweise die Möglichkeit zum lesenden und schreibenden Zugriff sowohl auf die Prozessorregister als auch auf den Systemspeicher. Durch die von einer OCD-Komponente bereitgestellte Infrastruktur ist demnach auch eine Injektion von Fehlern in das System möglich.

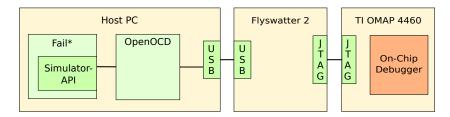

Ziel dieser Arbeit ist die Entwicklung und Untersuchung eines Fehlerinjektionssystems auf Basis von günstiger sogenannter *Commercial-Off-The-Shelf-*Hardware (kurz: COTS). Durch die Nutzung dieser Hardware ist es für Dritte bei geringem Aufwand

möglich, Forschungsergebnisse nachzuvollziehen und das System zu nutzen und zu erweitern. Es wird daher ein OCD-fähiges Hardware-Entwicklungsboard mit integriertem Prozessor, der üblicherweise in mobiler hochperformanter Verbraucherelektronik verwendet wird, an das bestehende Fehlerinjektions-Framework  $Fail^*$  (siehe [SHK<sup>+</sup>12]) angebunden. Im Kontext dieser Arbeit erhält das zu entwickelnde System den Projektnamen FailPanda. Das Framework Fail\* bietet bereits die zur Fehlerinjektion nötige Infrastruktur und eine generische Schnittstelle für neue Zielsysteme. Es werden hierzu die zur Fehlerinjektion nötigen Einzelfunktionen implementiert, wobei entstehende Probleme und mögliche Lösungen untersucht werden. Das System wird insbesondere auf Probleme der Performanz untersucht und diese werden mittels geeigneter Verfahren abgeschwächt, sodass die praktische Einsetzbarkeit gezeigt werden kann.

Die Arbeit ist wie folgt gegliedert. Kapitel 2 erläutert zunächst Grundlagen der Fehlerinjektion und stellt das Fehlerinjektions-Framework Fail\* vor. Anschließend wird in Kapitel 3 der im Zuge der Arbeit verfolgte Systementwurf auf Basis einer Anforderungsanalyse vorgestellt. Kapitel 4 schildert die Implementierung des Entwurfs und die Integration der entwickelten Verfahren in das Fehlerinjektions-Framework Fail\*. Das Gesamtsystem wird in Kapitel 5 hinsichtlich seiner Performanz evaluiert und es wird eine beispielhafte Generierung und Untersuchung von Fehlerinjektionsergebnissen gezeigt. Abschließend werden die Ergebnisse der Arbeit in Kapitel 6 zusammengefasst und es wird ein Ausblick auf mögliche Nachfolgearbeiten und Erweiterungen gegeben.

## 2 Grundlagen

Dieses Kapitel erläutert die in dieser Arbeit verwendeten Grundlagen nach aktuellem Stand der Forschung. Insbesondere wird auf Grundlagen der Fehlerinjektion eingegangen. In Abschnitt 2.1 werden zunächst die Grundbegriffe der Fehlerinjektion geklärt. Anschließend diskutiert Abschnitt 2.2 Fehlermodelle, die dem Verfahren zugrunde gelegt werden. In Abschnitt 2.3 werden Metriken vorgestellt, die statistische Aussagen über die Zuverlässigkeit eines Systems zulassen. Anschließend zeigt Abschnitt 2.4 einen Vergleich verschiedener Fehlerinjektionsverfahren. In Abschnitt 2.5 wird ein Verfahren zur Optimierung von Fehlerinjektionsexperimenten erläutert und schließlich wird in Abschnitt 2.6 das Fehlerinjektions-Framework Fail\* vorgestellt, das in dieser Arbeit verwendet wird.

### 2.1 Grundbegriffe der Fehlerinjektion

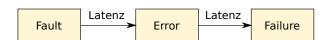

Der deutsche Begriff Fehler hat in diesem Zusammenhang mehrere Bedeutungen, die im Folgenden mithilfe der drei englischen Begriffe Fault, Error und Failure erläutert werden [KK07]. Abbildung 2.1 zeigt, dass ein Fault nach einer Latenz in einen Error umgewandelt und dieser wiederum nach einer weiteren Latenz zu einem Failure werden kann. Ein Fault repräsentiert das nicht vorhergesehene Verhalten einer Komponente, wobei dies sowohl eine Software- also auch Hardwarekomponente betreffen kann. Da im Kontext dieser Arbeit ausschließlich Fehler in Hardware-Komponenten untersucht werden, wird hier auf Software-Faults nicht weiter eingegangen. Ein beispielhafter Fault liegt in dem fehlerhaften Verhalten einer Speicherzelle aufgrund von externer hochenergetischer Einstrahlung [DNR02]. Solange dieses Verhalten keine Auswirkung auf den Systemzustand hat, bleibt der Fault ohne Auswirkung. Wird jedoch durch das fehlerhafte Verhalten beispielsweise ein Variablenwert ungewollt verändert, so wird aus einem Fault ein sogenannter Error. Errors können innerhalb des Systems propagieren, indem fehlerhafte Werte weiterverwendet werden. Führt ein Error zu nach außen sichtbarem fehlerhaftem Verhalten, so wird er zu einem Failure. Ein Beispiel für einen Failure ist ein fehlerhaftes Berechnungsergebnis oder ein Systemabsturz. Um im Folgenden eine deutsche Terminologie fortzuführen, wird ein Error als Fehler und ein Failure als Auswirkung eines Fehlers

Abbildung 2.1: Darstellung der Umwandlungsreihenfolge von Faults, Errors und Failures nach [BP03]. Es wird gezeigt, dass die Umwandlungsvorgänge nach einer Latenz aktiviert werden.

bezeichnet. Bei Beschreibungen physikalischer Vorgänge wird jedoch der Terminus Fault verwendet.

Fehlerinjektion ist die Simulation eines vorgegebenen Fehlermodells. Es steht im Gegensatz zu dem sogenannten Life Testing, wobei ein System im Realszenario beobachtet wird und die Fehler natürlich auftreten [BP03]. Das Verfahren des Life Testings benötigt im Allgemeinen deutlich mehr Zeit zur Aquirierung einer statistisch genügenden Menge von Ergebnissen als die Fehlerinjektion. Allerdings liegt der Vorteil darin, dass auf kein möglicherweise nicht hinreichendes Fehlermodell zurückgegriffen werden muss, da das Fehleraufkommen seinen statistischen Charakter implizit selbst definiert. Die Fehlerinjektion simuliert auf verfahrensabhängige Art und Weise (s. Abschnitt 2.4) das Auftreten von Fehlern, indem direkt auf die entsprechenden Komponenten eingewirkt wird.

Bei diesem Verfahren wird im Allgemeinen ein sogenannter Fehlerraum untersucht, welcher gültige Tupel aus Injektionszeitpunkt und -Ort repräsentiert und diesen eine Reaktion des Systems auf den entsprechenden Fehler zuordnet [BP03]. Die konkrete Ausprägung dieser Werte ist abhängig vom Injektionsverfahren und vom vorausgesetzten Fehlermodell. So wird im Verlauf dieser Ausarbeitung der Injektionszeitpunkt beispielsweise häufig als Position in einer Programmaufzeichnung, im Folgenden Trace genannt, definiert. Diese Position wird als dynamische Instruktion bezeichnet. Eine dynamische Instruktion ist eine konkrete Ausführung einer sogenannten statischen Instruktion. Während statische Instruktionen allein durch ihre Position im Programmcode beschrieben werden können (Instruktionsadresse), sind dynamische Instruktionen demnach die Ausführung dieser Instruktion zu einem bestimmten Zeitpunkt. Der Injektionsort kann beispielsweise ein Bit eines Speicherwortes repräsentieren.

Grundsätzlich wird davon ausgegangen, dass eine vollständige Abdeckung des Fehlerraums aufgrund der potenziell sehr hohen Anzahl nötiger Experimente nicht praktikabel durchführbar ist, weshalb im praktischen Einsatz sogenanntes Sampling verwendet

wird [BVFK05, BP03]. Mithilfe dieses Verfahrens werden Experimente für eine repräsentative Untermenge des Fehlerraums durchgeführt, indem gleichverteilt randomisiert

Experimente gewählt werden, bis eine Experimentmenge erreicht wurde, die mit dem

konkreten Verfahren in praktikabler Zeit durchführbar ist<sup>1</sup>.

Auf Basis der bekannten Parameter von Ort und Zeit wird die entsprechende Reaktion des Systems bemessen, um den Fehlerraum zu bestimmen. Aus einem solchen Ergebnis können direkt Schlüsse für den Entwurf von Fehlertoleranzverfahren gezogen werden, indem Häufungen von Fehlern gefunden werden [BSS13b]. Durch die Anwendung entsprechender Metriken kann das Fehlerverhalten quantifiziert werden, um einen Vergleich verschiedener Systeme durchführen zu können (s. Abschnitt 2.3).

Eine wichtige Grundannahme bei Fehlerinjektion ist der Determinismus des Zielsystems [SBK10]. Es wird davon ausgegangen, dass das System, solange keine Injektion erfolgt ist, sich in jeder Ausführung exakt gleich verhält. Wird ein System getestet, welches mit externen oder internen Quellen nichtdeterministischer Daten arbeitet (bei-

<sup>&</sup>lt;sup>1</sup>Eine weitere Einschränkung der Experimentmenge wird durch eine in Abschnitt 2.5 vorgestellte Technik erreicht, welche mehrere Fehlerinjektionsexperimente zu Äquivalenzklassen zusammenfasst, da a priori bekannt ist, dass die Ergebnisse aller Experimente einer solchen Klasse das gleiche Ergebnis produzieren werden.

2.1 Grundlagen

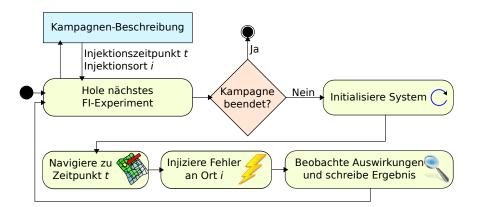

Abbildung 2.2: Schematische Darstellung des Ablaufs einer generischen Fehlerinjektionskampagne. Zur vereinfachten Darstellung wird hier nur von Einzelfehlern ausgegangen.

spielsweise Werte externer Sensoren), so müssen diese Quellen zunächst durch simulierte Quellen ersetzt werden, die typisches Verhalten deterministisch nachahmen [BP03].

Ist im Zielsystem der Determinismus erfolgreich hergestellt worden, so wird zunächst ohne Injektion von Fehlern eine Aufzeichnung eines fehlerfreien Programmablaufs durchgeführt, was als *Golden Run* bezeichnet wird. Wird das Verhalten der Plattform nach einer Fehlerinjektion mit dem Golden Run verglichen, so kann fehlerhaftes Verhalten identifiziert werden [BP03].

Mit einer Aufzeichnung des Programm-Trace ist es möglich, den Fehlerraum zu definieren. Hierbei werden üblicherweise die ausgeführten Instruktionen in der entsprechenden Ausführungsreihenfolge, ebenso wie die während der Programmaufzeichnung durchgeführten Zugriffe auf den Hauptspeicher, aufgezeichnet. Eine Einheit in der zeitlichen Dimension entspricht einer dynamischen Instruktion, welche durch ihre Position im Trace definiert ist. Die von der Zielapplikation verwendeten Ressourcen, wie beispielsweise die gelesenen Speicherwörter, ergeben kumulativ die Menge aller möglicher Injektionsorte. Soll ein Experiment bestimmen, ob das System nach einer Fehlerinjektion ein fehlerhaftes Ergebnis berechnet, so wird ein Vergleich mit dem Ergebnis aus dem Golden Run durchgeführt.

Die Zusammenfassung aller für die Abdeckung eines Fehlerraums nötigen Fehlerinjektionsexperimente wird nachfolgend als Kampagne bezeichnet [AVFK01]. Eine Kampagne umfasst eine Menge von einzelnen Fehlerinjektionsexperimenten, die den Fehlerraum in den Dimensionen Zeit und Ort definieren. Abbildung 2.2 schematisiert den Ablauf einer generischen Kampagne. Hierbei wurde zur einfacheren Darstellung die Einschränkung unternommen, dass in der Kampagne nur zu einem Zeitpunkt während der Ausführung ein Fehler injiziert wird. Der Ablauf einer Kampagne sieht vor, dass solange Parameter für das folgende Experiment von der Kampagne abgerufen werden, bis der Fehlerraum abgedeckt und die Kampagne beendet wurde.

Jedes Experiment hat den grundsätzlichen Aufbau, dass zunächst eine Systeminitialisierung erfolgt, welche von einer Ausführungsphase bis zum Injektionszeitpunkt t gefolgt

Abbildung 2.3: Allgemeine schematische Darstellung der Kampagnenverwaltung durch ein Fehlerinjektions-Framwork, übersetzt aus [HTI97].

wird. Diese Ausführungsphase wird nachfolgend als Navigation zum Injektionszeitpunkt bezeichnet. Anschließend wird am Injektionsort i ein Fehler injiziert und unter fortgesetzter Ausführung das Verhalten des Zielsystems untersucht. Gültige Ergebnisse können unterschiedlichster Form sein und sind im Kontext der jeweiligen Anwendung zu definieren. Beispielsweise können fehlerhafte Speicherzugriffe oder ausgelöste Prozessor-Traps zu möglichen Experimentergebnissen gehören. Das Ergebnis der Nachuntersuchung wird in der vorliegenden Repräsentation des Fehlerraums hinterlegt, um anschließend mit dem nächsten Experiment fortzufahren.

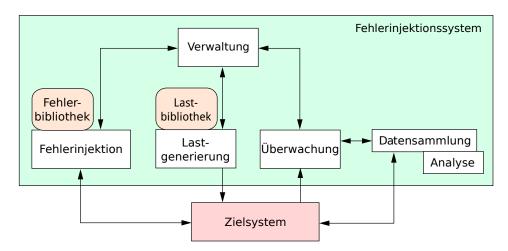

Die notwendige Verwaltung von derartigen Kampagnen wird von Fehlerinjektions-Frameworks bereitgestellt, die eine generische Definition von Experimenten ermöglichen [SBK10]. Derartige Frameworks bieten im Allgemeinen die in Abbildung 2.3 gezeigten Komponenten [HTI97]. Die Komponente der Fehlerinjektion führt zu den definierten Injektionszeitpunkten t eine Einfügung von Fehlern aus einer durch das Fehlermodell definierten Bibliothek in das Zielsystem durch. Gleichzeitig zur Ausführung des Zielsystems wird eine Last generiert, welche beispielsweise die Form der Ausführung eines Benchmarks oder der Übermittlung von definierten Eingaben haben kann. Die Last ist ebenfalls in Form einer Bibliothek vordefiniert. Eine Überwachungskomponente liest den aktuellen Zustand des Zielsystems aus und führt eine Sammlung von relevanten Zustandsdaten aus. Auf Basis der gesammelten Daten wird eine Analyse des Reaktionsverhaltens der Zielplattform auf die injizierten Fehler durchgeführt. Eine zentrale Verwaltung steuert schließlich die einzelnen Komponenten des Fehlerinjektionssystems. In Abschnitt 2.6 wird zur Erläuterung das Framework Fail\* detailliert beschrieben, da im Kontext der Arbeit darauf aufgebaut wird.

2.2 Grundlagen

### 2.2 Fehlermodelle

Bei der Fehlerinjektion werden Fehler unter einem gegebenen Modell simuliert. Dieses Modell beschreibt die Arten von Fehlern, von deren Auftreten ausgegangen wird und enthält eine statistische Beschreibung ihres Auftretens. Das Modell wird *a priori* definiert, indem Annahmen über die Fehleranfälligkeit der verschiedenen Systemkomponenten und eine statistische Beschreibung der durch die Ausführungsumgebung definierten Fehlerursachen berücksichtigt werden.

Grundsätzlich kann eine Einteilung in die Klassen der Hardware- und Software-Fehler durchgeführt werden. Während Hardware-Fehler beispielsweise durch Einstrahlung kosmischer Teilchen ausgelöst werden können, sind Software-Fehler die Folge fehlerhafter Programmierung [BP03]. Aus der Motivation dieser Arbeit geht hervor, dass im Kontext der Arbeit nur Hardware-Fehler betrachtet werden. Eine weitere Unterteilung in Fehlerklassen berücksichtigt transiente, permanente und unregelmäßig aktive Fehler [KK07]. Transiente Fehler werden auch als soft errors bezeichnet, da sie eine vorübergehende Störung des Systems, nicht jedoch den Defekt eines Bauteils beschreiben. Ein typischer transienter Fehler ist ein invertiertes Bit im Speicher, ausgelöst durch Strahlungseinfall [DNR02]. Wird die Speicherzelle nach Auftreten des Fehlers beschrieben, so ist der Fehler eliminiert. Permanente Fehler bezeichnen den Defekt eines Bauteils. So würde beispielsweise ein Bit im Speicher nach Auftreten eines solchen Fehlers aufgrund eines physischen Defekts in der Hardware immer eine logische Null darstellen. Schließlich bezeichnen unregelmäßig aktive Fehler einen dauerhaften Fehlerzustand wie bei den permanenten Fehlern, welcher allerdings nur zeitweise aktiv ist. Ein betroffenes Speicherbit würde beispielsweise zeitweise unregelmäßig im inaktiven Zustand des Fehlers eine korrekte Funktion aufweisen und bei Aktivität des Fehlers dauerhaft einen falschen Wert repräsentieren.

Da Hardware-Fehler je nach Injektionsverfahren auf verschiedenen Ebenen eines Systems wahrgenommen und injiziert werden können, wird im Fehlermodell spezifiziert, auf welcher Ebene die Untersuchung stattfindet. So kann das Fehlermodell beispielsweise Fehler auf Ebene von logischen Werten auf den Übertragungsleitungen oder auf Ebene von physikalischen Vorgängen innerhalb von Halbleitern eines Systems modellieren. In einer abstrakteren Betrachtung ist es möglich, Fehler auf Bit-Ebene in Speicher oder Registern vorzusehen [BP03]. Die Wahl eines Injektionsverfahrens (s. Abschnitt 2.4) definiert implizit die Ebene der möglichen auftretenden Fehler, wodurch wiederum das Fehlermodell eingeschränkt wird. Im Kontext dieser Arbeit werden ausschließlich Fehler auf Bit-Ebene betrachtet, sodass auf Instruktionsebene eine Modifikation der Werte vorgenommen werden kann.

Das Fehlermodell bestimmt direkt die Form der Fehlerinjektion. So wird beispielsweise ein Experiment unter der Annahme von Einzelfehlern das Zielsystem in den Zustand des Fehlerzeitpunktes bringen, einen Fehler an dem untersuchten Fehlerort injizieren und das System weiter ausführen lassen und dabei auf fehlerhaftes Verhalten untersuchen (s. Abb. 2.2). Im Gegensatz dazu müsste unter der Voraussetzung, dass Fehler in sogenannten Bursts auftreten, gleichzeitig an mehreren benachbarten Fehlerorten injiziert

werden [HSR95]. Würde das Modell einen zeitlichen Burst vorsehen, so würde ab der ersten Fehlerinjektion das Zielsystem mehrfach an aufeinander folgenden Instruktionen angehalten, um weitere Fehler injiziert werden.

Mathematische Beschreibungen für das Auftreten von Hardware-Fehlern sind mithilfe von statistischen Modellen möglich. Häufig werden zu diesem Zweck Poisson-Prozesse eingesetzt [KK07]. Sie beschreiben allgemein die Auftretenswahrscheinlichkeiten von nichtdeterministischen Ereignissen in einem bestimmten Zeitraum. Somit kann mit einer entsprechend parametrisierten Poisson-Verteilung die Wahrscheinlichkeit für das Auftreten von Fehlern modelliert werden. Die Verteilung gibt für einen angegebenen Zeitraum und eine angegebene Anzahl erwarteter Fehler einen Wahrscheinlichkeitswert an. Häufig fällt die Verteilung für steigende Fehlerzahlen sehr stark ab, sodass die Wahrscheinlichkeiten für mehr als einen Fehler im betrachteten Zeitraum mit dem Wert Null angenommen werden. Durch diese Annahme lässt sich begründen, dass Fehlerinjektionskampagnen, die nur Einzelfehler betrachten, eine gute Annäherung an die Realität bieten.

### 2.3 Zuverlässigkeitsmetriken

Um eine Auswertung der Ergebnisse einer Fehlerinjektions-Kampagne durchführen zu können, existieren Metriken, durch deren Anwendung Aussagen über verschiedene Eigenschaften des Zielsystems getroffen werden können. Durch Verwendung geeigneter Metriken ist der Vergleich zweier Systeme möglich, sodass beispielsweise ein System ohne Einsatz von Fehlertoleranz mit der entsprechenden um eine Fehlertoleranzmaßnahme erweiterten Version verglichen werden kann. Im Folgenden werden einige typische Metriken und deren jeweilige Aussage über das getestete System vorgestellt.

Da Fehlerinjektion üblicherweise eingesetzt wird, um die Zuverlässigkeit (engl.: Reliability) eines Systems unter der Annahme des Auftretens von Fehlern zu bestimmen, ist diese Metrik als zentral anzusehen. Die Zuverlässigkeit R ist als

$$R = 1 - P$$

{Failure}

definiert. Das bedeutet, dass die Zuverlässigkeit die Gegenwahrscheinlichkeit zur Wahrscheinlichkeit eines nach außen sichtbaren Fehlers unter einem gegebenen Fehlermodell ist [AAA $^+$ 90]. Durch diese Definition erweitert sich die Formel nach den zuvor beschriebenen englischen Fehler-Terminologien zu

$$R = 1 - (P \{Failure | Fault\} \cdot P \{Fault\})$$

$[AAA^+90]$ . Die Wahrscheinlichkeit P {Fault} wird durch das Fehlermodell definiert und ist a priori bekannt. P {Failure|Fault} ist die Wahrscheinlichkeit für das nach außen sichtbare fehlerhafte Verhalten des Systems unter der Voraussetzung, dass ein Fehler nach dem definierten Modell injiziert wurde. Diese Wahrscheinlichkeit ist unter Zuhilfenahme von Fehlerinjektion empirisch zu bestimmen. Zu diesem Zweck wird die Gesamtmenge aller Fehlerinjektionsexperimente durch Division in ein Verhältnis zu der

2.4 Grundlagen

Menge an Experimenten mit fehlerhaftem Ausgang gesetzt. Es wird demnach der Anteil an Experimenten bemessen, welcher von einem auf dem System operierenden Fehlertoleranzverfahren nicht beseitigt werden konnte. Wird diese Metrik verwendet, um zwei verschiedene Fehlertoleranz-Konfigurationen eines Systems zu vergleichen, so ergeben sich allerdings die nachfolgend erläuterten Probleme.

Bei der Erweiterung einer Applikation um eine Fehlertoleranzmaßnahme zeigt sich der Nebeneffekt, dass zusätzliche Ressourcen verwendet werden. So wird üblicherweise die Laufzeit des Programms verlängert und es werden weitere Speicherbereiche verwendet. Hierdurch vergrößert sich der Fehlerraum, dessen Größe in P {Failure|Fault} einfließt. Somit kann der Wert von R vergrößert werden, indem ein Verfahren eingebracht wird, welches lediglich eine Vergrößerung des Fehlerraums erwirkt, ohne tatsächlich Fehler abzufangen. Beispielsweise ist ein Verfahren vorstellbar, welches einige nop-Instruktionen in einen Benchmark einbringt. Der Vergleich der Werte von R für das Programm ohne und mit eingebrachtem Verfahren würde eine Verbesserung zeigen, obwohl tatsächlich keine Fehlerbehandlung durchgeführt wird.

Es konnte somit gezeigt werden, dass R zwar für absolute Aussagen zur Zuverlässigkeit verwendbar ist, jedoch für den Vergleich von Fehlertoleranzmaßnahmen unbrauchbar ist. Um einen quantitativen Vergleich der Zuverlässigkeit zweier Varianten eines Zielsystems durchzuführen, sind absolute Anzahlen der Failures zu verwenden [BSS13a]. Hierbei kann das Ergebnis nur verbessert werden, indem auftretende Fehler von einer Fehlertoleranzmaßnahme erfolgreich behandelt werden.

Für die statistische Quantisierung der Eigenschaften eines untersuchten Systems existieren noch weitere Metriken, die allerdings im Kontext dieser Arbeit keine Verwendung finden. Daher werden wichtige Metriken an dieser Stelle nur kurz genannt. Die Verfügbarkeit (engl.: Availability) bezeichnet die Wahrscheinlichkeit dafür, dass ein System zu einem Zeitpunkt t zur Verwendung bereit steht, d.h. korrekt funktioniert und auf Anfragen reagiert [BP03]. Mit der Metrik der Sicherheit (engl.: Safety) wird die Wahrscheinlichkeit beschrieben, mit der ein System entweder im Zustand der korrekten Ausführung ist, oder alternativ seine Funktion einstellt, um eine Propagation eines Fehlers durch das Gesamtsystem zu verhindern. Dieses Verhalten wird auch als fail-stop behaviour bezeichnet [BSS13b]. Die mittlere Zeit bis zum Auftreten eines Fehlers (engl.: Mean Time To Failure (kurz: MTTF)) bezeichnet für dauerhaft operierende Systeme die mittlere Zeitspanne, bis zu der ein fehlerhaftes Verhalten des Systems unter Einwirkung von Fehlern erwartet wird.

### 2.4 Fehlerinjektionsverfahren

Dieser Abschnitt vermittelt einen Überblick über die verschiedenen existierenden Verfahren zur Injektion von Hardware-Fehlern in ein Zielsystem und grenzt diese voneinander ab. Die Verfahren werden anhand folgender Aspekte, angelehnt an die Untersuchungen in [PGLOVE11], verglichen:

| Tabelle 2.1: | Vergleich | $\operatorname{der}\operatorname{im}$ | Kontext | ${\rm dieser}$ | Arbeit | be trachteten | Fehlerinjektions | sverfah- |

|--------------|-----------|---------------------------------------|---------|----------------|--------|---------------|------------------|----------|

|              | ren.      |                                       |         |                |        |               |                  |          |

|                             | Hardware-<br>basiert          | Software-basiert                               | Simulator-<br>basiert              | OCD-basiert                              |  |

|-----------------------------|-------------------------------|------------------------------------------------|------------------------------------|------------------------------------------|--|

| Änderung des<br>Zielsystems | keine                         | hoch                                           | keine                              | gering                                   |  |

| Geschwindig-<br>keit        | hoch                          | hoch                                           | gering                             | hoch                                     |  |

| Parallelisier-<br>barkeit   | gering                        | gering                                         | hoch                               | gering                                   |  |

| Kosten                      | sehr hoch                     | gering                                         | gering                             | hoch                                     |  |

| Fehlermodell                | grundsätzlich<br>unbeschränkt | nur per Software<br>zugreifbare<br>Komponenten | nur simulierte<br>Komponen-<br>ten | nur per OCD<br>zugreifbare<br>Komponeten |  |

- Nötige Veränderung des Zielsystems: Je geringer die nötigen Veränderungen des Zielsystems für die Anwendung des betrachteten Verfahrens sind, umso höher ist die Aussagekraft der Ergebnisse. Ist für das Injektionsverfahren beispielsweise ein Eingriff in den Programmcode nötig, so wird das Verhalten des Zielsystems unter Umständen erheblich verändert, wodurch die Aussagekraft der Ergebnisse sinkt.

- Geschwindigkeit: Aufgrund der typischerweise hohen Größe des Fehlerraums müssen Einzelexperimente möglichst schnell durchgeführt werden können, damit eine komplette Abdeckung des Fehlerraums in praktikabler Zeit ermöglicht ist.

- Parallelisierbarkeit: Um mögliche Defizite in der Ausführungsgeschwindigkeit zu kompensieren, kann es wichtig sein, mehrere Fehlerinjektionsexperimente parallel auszuführen. Aus diesem Grund wird auch die Möglichkeit zur Parallelisierung der Verfahren untersucht.

- Kosten: Die betrachteten Injektionsmaßnahmen generieren unterschiedliche finanzielle und entwicklungsspezifische Kosten. Je geringer die Kosten für den Einsatz eines Verfahrens sind, umso geringer ist auch die Einstiegshürde für potenzielle Anwender.

- Fehlermodell: Verschiedene Fehlerinjektionsverfahren schränken das Fehlermodell bezüglich der fehlersensitiven Komponenten des Zielsystems und der Art von injizierbaren Fehlern ein. Da diese Einschränkung bei der Wahl eines Verfahrens aufgrund des a priori definierten Fehlermodells Verfahren disqualifizieren kann, wird ebenfalls anhand dieses Kriteriums verglichen.

2.4 Grundlagen

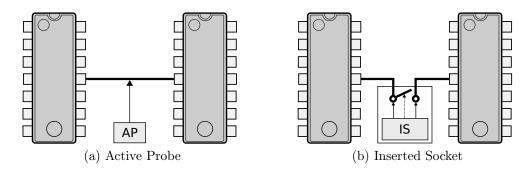

Abbildung 2.4: Schematische Darstellung der Funktionsweise von Active Probes und Inserted Sockets nach [BP03].

Eine Übersicht zur Einordnung der nachfolgend betrachteten Verfahren wird in Tabelle 2.1 gezeigt. Einzelne Komponenten der Tabelle werden in den jeweiligen Untersuchungen erläutert.

#### 2.4.1 Hardware-basiert

Bei Hardware-basierter Fehlerinjektion handelt es sich grundsätzlich um ein Verfahren, welches eine zusätzliche Hardwarekomponente dazu einsetzt, das ansonsten unveränderte Zielsystem zu stören [HTI97]. Hierbei wird zwischen kontaktbehafteter und kontaktloser Injektion unterschieden. Bei der kontaktbehafteten Fehlerinjektion werden üblicherweise auf Ebene der Ein-/Ausgabe-Kontakte des zu untersuchenden Chips mit sogenannten Active Probes oder Inserted Sockets fehlerhafte Zustände eingestreut [BP03]. Mittels dieser Schnittstelle können Fehler gezielt an einigen internen Komponenten des Zielsystems injiziert werden und somit sind potenziell Fehlerorte möglich, die per Software nicht zugreifbar sind. Abbildung 2.4 zeigt schematisch den Aufbau bei Einsatz der Verfahren. Active Probes (s. Abb. 2.4a) werden dazu eingesetzt, fehlerhafte Ströme an zugreifbaren Ubertragungsleitungen anzulegen, um Veränderungen der logischen Zustände an den Kontakten herbeizuführen. Active Probes können nicht auf den augenblicklichen Zustand des Ein-/Ausgabe-Kontakts reagieren. Inserted Sockets (s. Abb. 2.4b) werden hingegen als Brücke zwischen die Chip-Kontakte und die angeschlossene Hardware geschaltet und können so komplexere logische Veränderungen wie Invertierungen der Signale durchführen.

Im Gegensatz zu den kontaktbehafteten Verfahren simulieren kontaktlose Verfahren die realen Ursachen für Fehler wie beispielsweise Strahlungspartikel oder elektrische Felder. Das zu untersuchende System wird der Fehlerquelle ausgesetzt, welche eine realitätsgetreue Umgebung, wie beispielsweise den Einsatz im Weltraum, simuliert. Hierbei wird die Auftretenswahrscheinlichkeit von Fehlern durch Intensivierung der Bedingungen erhöht, um im Gegensatz zum Life Testing schneller eine statistisch ausreichende Datenmenge generieren zu können [BP03]. Bei dieser Technik kann allerdings weder Ort noch Zeit der auftretenden Fehler exakt gesteuert werden, wodurch sich das Verfahren nur für statistische Aussagen über den Betrieb unter den simulierten Bedingungen

eignet. Es können keine Untersuchungen der Fehleranfälligkeit einzelner Komponenten durchgeführt werden.

Aufgrund der Durchführung auf der echten Hardware ohne ein nötiges Anhalten des Systems ist dieses Verfahren sehr schnell. Die Hardware-Fehlerinjektion setzt keine Modifikation des Programmcodes voraus, wodurch die Ergebnisse eine sehr hohe Aussagekraft haben. Da die parallele Ausführung von Experimenten pro Ausführungseinheit sowohl ein Exemplar der Zielhardware als auch die gesamte Injektions-Infrastruktur erfordert, ist die Parallelisierbarkeit stark beschränkt. Die Kosten des Verfahrens sind durch den Einsatz von spezialisierter Injektions-Hardware als hoch zu betrachten. Hardware-Fehlerinjektion ist für den Einsatz unter Fehlermodellen geeignet, die keine konkrete Vorgabe zu Ort oder Art von möglichen Fehlern treffen, da das Fehlermodell implizit durch die Kombination aus realitätsnaher Umgebung und echter Hardware definiert ist.

#### 2.4.2 Software-basiert

Bei Software-basierter Fehlerinjektion handelt es sich um ein Verfahren, welches eine Fehlerinjektion auf Code-Ebene durchführt [HTI97]. Es lässt sich eine Einteilung in die Klassen der Injektion zur Kompilierungszeit und der Injektion zur Laufzeit durchführen. Bei der Fehlerinjektion zur Kompilierungszeit werden vor Ausführung des Programms Fehler in den Code eingestreut. Somit lassen sich nur Fehler simulieren, die seit Anfang der Programmausführung bestehen, wodurch das Verfahren stark beschränkt ist. Bei der Injektion zur Laufzeit wird hingegen zusätzlicher Code eingefügt, welcher eine Fehlerinjektion zum spezifizierten Zeitpunkt durchführt. Der Injektionszeitpunkt kann mittels Zeitmessung, Ausnahmebehandlungen oder direkte Injektion der Fehlerinjektions-Routine an die Zielinstruktion erreicht werden. Es kann aber beispielsweise auch ein Verfahren gewählt werden, bei dem ein zusätzlicher Programm-Faden zufällige Fehler einstreut, wenn ein der kontaktlosen Hardware-Fehlerinjektion ähnliches Verfahren simuliert werden soll [HESM10].

Software-Fehlerinjektion ist ein kostengünstiges Verfahren, da auf zusätzliche Hardware verzichtet wird und die Entwicklungszeit für das Injektionsverfahren als gering eingestuft werden kann. Weil das Zielsystem bei diesem Verfahren durch die Modifikation des Programmcodes stark verändert wird, ist die Aussagekraft der Ergebnisse allerdings beschränkt. Die Injektionsorte sind im Gegensatz zur Hardware-Fehlerinjektion auf die per Software zugreifbaren Komponenten beschränkt. Verwendbare Fehlermodelle sehen invertierte Bits in Speicher und Registern vor. Da die Software-Fehlerinjektion auf der unveränderten Zielplattform operiert, ist die Ausführungsgeschwindigkeit wie im Fall der Hardware-Fehlerinjektion hoch und die Parallelisierbarkeit gering.

#### 2.4.3 Simulator-basiert

Die Simulator-basierte Fehlerinjektion basiert auf dem Ansatz, die Hardware-Plattform des Zielsystems durch eine Softwarekomponente nachzubilden und Fehler in die simulierten Komponenten zu injizieren [BP03]. Zu diesem Zweck wird der Programmcode des Simulators modifiziert, nicht jedoch der Code der darin ausgeführten Zielapplikation. Da

2.4 Grundlagen

ein Simulator grundsätzlich die Hardware-Komponenten wie Speicher und Prozessorregister in Variablen umwandelt und die Ausführung des Prozessors durch Funktionen ersetzt, die mit diesen Zustandskomponenten arbeiten, ist ein voller Zugriff auf alle simulierten Komponenten möglich [JAR<sup>+</sup>94]. Dies gilt insbesondere, wenn der Simulator quelloffen verfügbar ist, sodass direkte Modifikationen im Simulationscode durchgeführt werden können, um Fehler in die Komponenten zu injizieren.

Grundsätzlich können Hardware-Simulatoren das Verhalten des simulierten Systems auf unterschiedlicher Detailebene nachbilden. Beispielsweise bietet der Simulator Gem5 explizit Prozessormodelle verschiedener Detailgrade für die gleiche Plattform, um dem Nutzer die Wahl zwischen Detailgrad und Ausführungsgeschwindigkeit zu ermöglichen [BBB+11]. Da das Systemmodell allerdings stets von der echten Hardware abstrahiert und insbesondere in durch injizierte Fehler ausgelösten Ausnahmefällen in seinem Verhalten von der Hardware abweichen kann, sind die Ergebnisse der Simulator-basierten Fehlerinjektion weniger realitätsgetreu als die Injektion im korrespondierenden echten System.

Da Hardware-Simulatoren üblicherweise eine deutlich reduzierte Ausführungsgeschwindigkeit gegenüber der simulierten Hardware aufweisen, ist dieses Verfahren als langsam einzustufen. Dieses Geschwindigkeitsdefizit kann jedoch mittels der Möglichkeit zur hoch-parallelen Ausführung abgemildert oder kompensiert werden. Simulator-basierte Fehlerinjektion erfordert keine Modifikationen der Zielsoftware und ist aufgrund der reinen Durchführung in Software kostengünstig im Betrieb. Auch die Implementierung Simulator-basierter Fehlerinjektion ist als günstig anzusehen, da Komponenten im Falle von quelloffenen Simulatoren unmittelbar zugreifbar sind [JAR<sup>+</sup>94]. Der Detailgrad des simulierten Modells bedingt direkt die Art von injizierbaren Fehlern. So sind teilweise in Simulatoren einige Hardware-Komponenten wie beispielsweise Caches nicht berücksichtigt, weshalb hier keine Injektion durchgeführt werden kann. Andererseits ist es bei sehr detaillierten Modellen möglich, an mehr Stellen zuzugreifen, als es typischerweise mittels Software auf der Plattform möglich.

#### 2.4.4 OCD-basiert

On-Chip Debugger (kurz: OCD) sind eine im Bereich aktueller Mikrocontrollersysteme weit verbreitete Einrichtung, welche es ermöglicht, die Programmausführung von einem externen Hostrechner per Software zu stoppen und Prozessorregister sowie Speicher auszulesen und zu beschreiben [FGAF06]. Zudem bieten typische OCD die Möglichkeit, Breakpoints zu setzen, sodass die Ausführung beim Laden der definierten Instruktion angehalten wird. Komplexere OCD bieten zusätzlich die Möglichkeit, Datenhaltepunkte (sog. Watchpoints) anzulegen, die bei einem Speicherzugriff an einer definierten Speicherstelle das System anhalten. Des Weiteren bieten einige OCD komplexere Funktionalitäten, wie beispielsweise die Aufzeichnung eines Programm-Trace [FGAF06] oder die Definition von Nebenbedingungen für Haltepunkte, wie beispielsweise das Anhalten nach einer festen Anzahl an Ausführungen einer Instruktion [SBK10].

OCD wird üblicherweise für die Fehlersuche – das sogenannte *Debugging* – in dem auf der Hardware ausgeführten Programmcode genutzt, was insbesondere im Bereich ein-

gebetteter Hardware aufgrund fehlender Schnittstellen wichtig ist. Das Debugging wird in Software von einem externen Rechner gesteuert, der dem Anwender eine komfortable Schnittstelle bietet.

Aufgrund des Funktionsumfangs von OCD wird eine Fehlerinjektion durch angebundene Steuerungssoftware ermöglicht. Hier kann insbesondere eine Injektion in Speicher und Prozessorregister durchgeführt werden. Die Definition der Injektionszeitpunkte ist durch die Verwendung von Haltepunkten möglich.

Typischerweise wird ein OCD mithilfe eines sogenannten *Debuggers*, einer zusätzlich als Kommunikationsverbindung nötigen Hardware, an einen Hostrechner angebunden. Da die Datenverbindung zwischen Hostrechner und OCD über den Debugger im Allgemeinen eine hohe Datenumlaufzeit aufweist, wird häufig die Steuerung des OCD in einer Spezialhardware – beispielsweise einem FPGA – direkt realisiert [MEEM12, PGLOGVE07, FAF06b]. Wird eine standardisierte OCD-Schnittstelle – wie beispielsweise JTAG – verwendet, so ist das Fehlerinjektionssystem für verschiedene Prozessoren verwendbar [FGAF06].

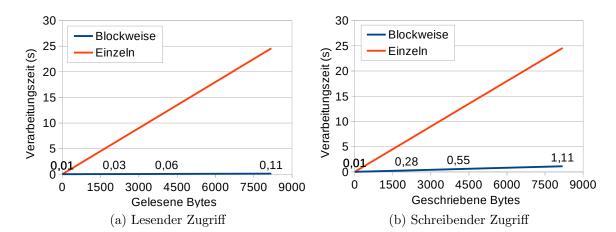

OCD-basierte Fehlerinjektion weist im Regelfall eine hohe Ausführungsgeschwindigkeit für Experimente auf, was darauf beruht, dass die Hardware den Programmcode in voller Geschwindigkeit ausführen kann. Durch das zeitweise Anhalten des Systems, beispielsweise für die Injektion von fehlerhaften Werten, wird allerdings die Performanz reduziert. Die durch OCD-basierte Fehlerinjektion gewonnenen Ergebnisse weisen eine hohe Realitätstreue auf, da im Allgemeinen keine Modifikation der Hardware oder des darauf laufenden Softwaresystems durchgeführt werden muss, um das Verfahren zu realisieren [FSK98]. Aufgrund der nötigen Verwendung von zusätzlicher Hardware zur Realisierung des Zugriffs auf OCD-Funktionen ist das Verfahren als nicht kostengünstig einzuordnen. Aus diesem Grund ist auch die Parallelisierbarkeit beschränkt, da für jede zur Fehlerinjektion verwendete Systemeinheit tatsächliche Hardware verwendet wird. Realisierbare Fehlermodelle sind auf die per OCD zugreifbaren Komponenten der Hardware beschränkt. Diese decken sich üblicherweise in Großteilen mit den per Software zugreifbaren Systemanteilen.

### 2.5 Optimierung von Fehlerinjektionsexperimenten

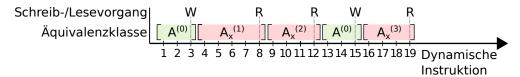

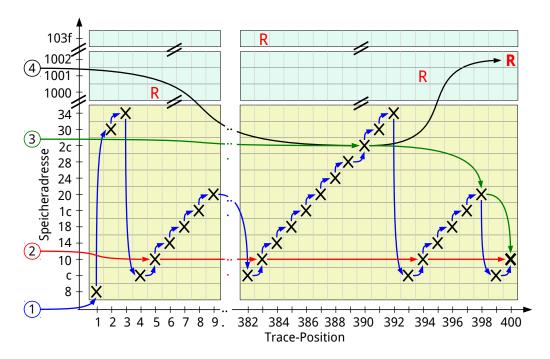

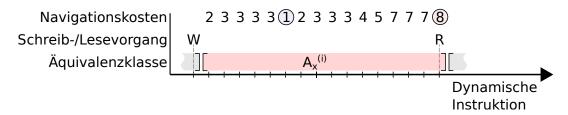

Die Abdeckung eines spezifischen Fehlerraums bedarf im Allgemeinen einer Anzahl an Experimenten, die sich aus der Multiplikation der Länge des Traces mit der Anzahl der Injektionsorte ergibt und demnach schnell stark wächst. Aus diesem Grund ist eine Reduktion der Anzahl durchzuführender Experimente notwendig, damit die Laufzeit einer Kampagne nicht impraktikabel wird. Das sogenannte Fault-Space Pruning nach dem Def-Use-Prinzip kann bei Fehlerinjektion in Speicher oder Registern eingesetzt werden [BVFK05]. Hierbei werden alle im Trace befindlichen Zugriffe auf ein spezifisches Speicherwort bzw. Register mit der Adresse x betrachtet und wie in Abbildung 2.5 zu Äquivalenzklassen zusammengefasst, die nachfolgend mit  $A_x^{(y)}$  bezeichnet werden. Hierbei bezeichnet y einen Index für die Menge aller Äquivalenzklassen innerhalb eines Traces für den Injektionsort x.

2.6 Grundlagen

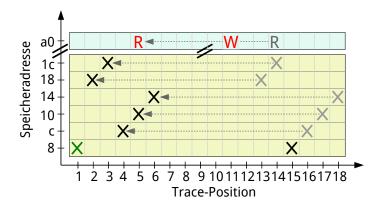

Abbildung 2.5: Schematische Darstellung der Zusammenfassung von Fehlerinjektionsexperimenten zu Äquivalenzklassen für ein Speicherwort oder Register. Die auf dem betrachteten Injektionsort durchgeführten Schreibvorgänge sind mit einem "W" und die Lesevorgänge mit einem "R" gekennzeichnet. Die Äquivalenzklassen mit a priori bekanntem Ergebnis sind grün eingezeichnet und die Äquivalenzklassen, für die ein einzelnes Experiment durchgeführt werden muss, sind rot eingezeichnet.

Aufgrund der Betrachtung von Paaren aufeinander folgender Schreib-/Lesevorgänge (definiert durch  $t_l$  für die linke und  $t_r$  für die rechte dynamische Instruktion) ergeben sich zwei Fälle in Abhängigkeit von dem nachfolgenden Schreib- oder Lesevorgang [BRIM98]:

- 1. Lesevorgang: Ist der nachfolgende Zugriff ein Lesevorgang, wie im Beispiel der dynamischen Instruktionen  $t_l = 3$  und  $t_r = 8$  in Abbildung 2.5, so werden alle Instruktionen aus dem Intervall  $(t_l; t_r]$  zu einer Äquivalenzklasse zusammengefasst (in diesem Fall zur Äquivalenzklasse  $A_x^{(1)}$ ). Für eine solche Äquivalenzklasse wird ein einziges Repräsentativexperiment zu einem beliebigen Injektionszeitpunkt innerhalb der Klasse durchgeführt und im Ergebnisraum für alle Elemente der Klasse eingetragen. Dieser Zusammenschluss ist gültig, da der injizierte Wert zum Zeitpunkt  $t_r$  gelesen wird und sich daher erst zu diesem Zeitpunkt auswirken kann.

- 2. Schreibvorgang: Ist der nachfolgende Zugriff ein Schreibvorgang, wie bei den dynamischen Instruktionen  $t_l = 12$  und  $t_r = 15$ , so werden alle Instruktionen, in dem Intervall  $(t_l; t_t]$  der Äquivalenzklasse  $A^{(0)}$  hinzugefügt, welche alle a priori als fehlerfrei bekannten Experimente beinhaltet. Dieses Vorgehen ist korrekt, da bei Injektion zu einem beliebigen Zeitpunkt in dem Intervall in das betrachtete Speicherwort oder Register der fehlerhafte Wert nicht gelesen, sondern vor dem nächsten Lesevorgang wieder beschrieben wird.

Da die Zusammenfassung von Äquivalenzklassen auf Ebene von Speicherwörtern und Registern durchgeführt wird, wird für jede Äquivalenzklasse  $A_x^{(y)} \neq A^{(0)}$  nach dem entsprechenden Fehlermodell eine Menge von Fehlerinjektionsexperimenten durchgeführt, beispielsweise ein Experiment für jedes enthaltene Bit.

Weil die Anzahl durchgeführter Injektionsexperimente durch das Pruning potenziell stark reduziert wird, müssen die Meta-Informationen über angelegte Äquivalenzklassen in die Berechnung der Metriken mit einfließen, indem eine Rücktransformation für jedes Injektionsergebnis in den Fehlerraum mithilfe der Informationen über die geltende Äquivalenzklasse durchgeführt wird.

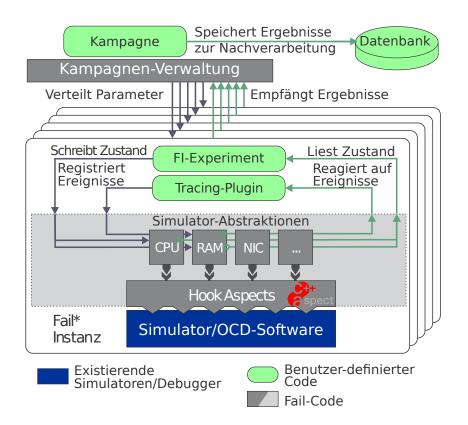

Abbildung 2.6: Schematische Darstellung der Fail\*-Architektur für Simulatoren und OCD-angebundene Hardware, modifiziert aus [SHK+12].

### 2.6 Das Fehlerinjektions-Framework Fail\*

Bei Fail\* handelt es sich um ein Fehlerinjektionswerkzeug, welches im Kontext des DanceOS-Forschungsprojekts entwickelt wird [SHK<sup>+</sup>12]. Es ist auf Simulator-basierte und OCD-basierte Fehlerinjektion ausgelegt. Die Ausführungsplattform, in die Fail\* Fehler injiziert, wird in diesem Kontext als Backend bezeichnet. Die Kernkonzepte von Fail\* gliedern sich in folgende Aspekte:

- Parallelität: Durch die Verwendung einer Client/Server-Architektur wird eine verteilte Durchführung mehrerer Injektionsexperimente zeitgleich ermöglicht. Mit diesem Verfahren lässt sich, insbesondere bei der Verwendung von Simulator-Backends, ein hoher Durchsatz an Experimenten erreichen.

- Generische Experimente: Experimenten wird eine generische Kontrollschnittstelle zur Verfügung gestellt, um Einschränkungen bezüglich des Fehlermodells zu minimieren. Es können Ereignisse wie das Erreichen bestimmter Instruktionen oder die Auslösung eines Traps registriert werden und direkte Zustandsänderungen wie das Schreiben in Speicher oder Register durchgeführt werden.

2.6 Grundlagen

• Generische Backend-API: Durch die Nutzung einer generischen Schnittstelle zu Simulatoren oder Hardware-Debuggern lässt sich das System leicht um neue Backends erweitern. Gleichfalls wird dadurch ermöglicht, Experimentcode für verschiedene Backends wiederzuverwenden.

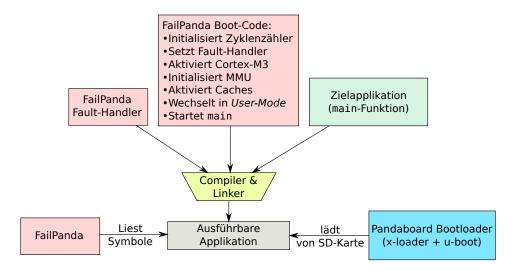

Abbildung 2.6 zeigt die grundlegende Architektur von Fail\* gegliedert in ein Modul für die Verwaltung von Kampagnen, eine Datenbank als Parameter- und Ergebnisspeicher und mehrere Module zur Ausführung der Einzelexperimente. Das *Tracing-Plugin* dient einer initialen Aufzeichnung der Programmausführung zur Definition des Fehlerraums und für die im vorherigen Abschnitt beschriebene Reduktion der Experimentmenge.

Der Benutzer entwickelt eine spezialisierte Kampagne, welche eine spezifische Menge an Experimentparametern an die Fail\*-Instanzen verteilt. Es werden benutzerdefinierte Experimente auf Basis der empfangenen Parameter durchgeführt, welche die eigentliche Fehlerinjektion in dem spezifischen Backend durchführen. Zu diesem Zweck wird einem Experiment eine Simulator-Abstraktionsschnittstelle zur Verfügung gestellt, welche Zugriff auf im Zielsystem vorhandene Hardware wie Register und Speicher erlaubt.

Die konkrete Implementierung dieser Schnittstelle geschieht üblicherweise mittels sogenannter *Hook-Aspects*, die Code zur Modifikation und Registrierung von Ereignissen in die konkrete Simulatorsoftware oder alternativ die OCD-Steuerungssoftware an den erforderlichen Stellen einsetzt. Mittels der Nutzung von Aspekten lässt sich die nötige Modifikation des Zielcodes minimieren und es ist eine Trennung der Belange möglich, sodass der eingefügte Code separat von der Zielsoftware gekapselt werden kann. Die konkrete Implementierung erfolgt mithilfe der C/C++-Spracherweiterung *AspectC*++, welche aspektorientierte Programmierung ermöglicht [SLU05].

Im Folgenden wird detailliert auf wichtige Konzepte von Fail\* eingegangen. Hierzu beschreibt Abschnitt 2.6.1 zunächst die Backend-Abstraktion, welche eine einfache Erweiterung des Verfahrens um neue Simulator- und OCD-basierte Backends ermöglicht. Anschließend wird das verteilte Kampagnen-Management von Fail\* in Abschnitt 2.6.2 erläutert.

#### 2.6.1 Backend-Abstraktion

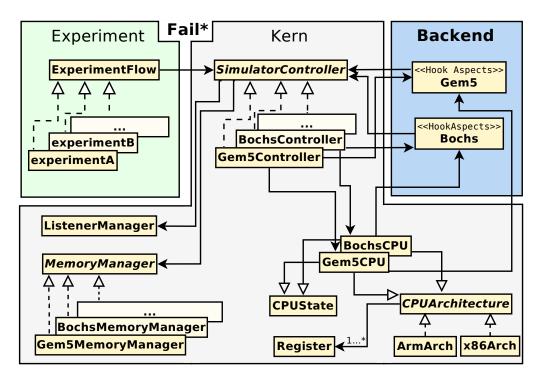

Abbildung 2.7 zeigt eine abstrakte Darstellung der Komponentenstruktur von Fail\* in Form eines Klassendiagramms. Die Darstellung ist grundlegend in die zwei Teile der Fail\*- und der Backend-Komponenten aufgeteilt. Innerhalb der Fail\*-Komponenten wurde weiterhin nach Experiment- und Kern-Komponenten aufgeteilt. Die Anbindung der bislang in Fail\* integrierten Simulator-Backends Bochs (x86-Simulation) und Gem5 (im Fail\*-Kontext für die Simulation von ARM-Backends verwendet) ist hier beispielhaft demonstriert. Die Abbildung macht zunächst deutlich, dass sowohl Experimente, als auch Backends die generische Schnittstelle des SimulatorControllers verwenden. Dieser wird durch konkrete Controller der einzelnen Backends implementiert und bietet Zugriff auf Komponenten wie den MemoryManager und die Backend-CPU. Somit sind konkrete Komponenten, wie die Prozessor-Register und der Speicher eines Backends, über eine generische Schnittstelle zugänglich.

Abbildung 2.7: Abstrakte Darstellung der relevanten Schnittstellen für Experimente und Backends in Fail\* als Klassendiagramm. Es wurde eine grobe Modularisierung in Fail\*-Komponenten (Kern (grau) und Experiment (grün)), sowie Backend-Komponenten (blau) vorgenommen.

Aufgrund dieser Architektur wird eine Konfigurierbarkeit realisiert, die für ein unverändertes Experiment den einfachen Austausch des zugehörigen Backends ermöglicht. Die konkrete Backend-Komponente wird von den Implementierungen der generischen Schnittstellen angesprochen. Für die Propagation von Informationen des Backends zum Experiment stehen wiederum Schnittstellen im SimulatorController zur Verfügung, die eine einfache Anbindung neuer Backends ermöglichen. Im Folgenden werden einzelne Komponenten detaillierter diskutiert.

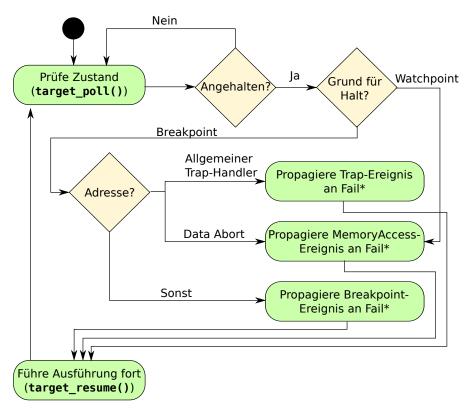

Der in Abbildung 2.7 aufgeführte ListenerManager implementiert eine zentrale Funktionalität in Fail\*. In einem Experiment ist es möglich, mittels einer beliebigen Anzahl an aktuell aktiven EventListenern – also Komponenten, die eine Benachrichtigung bei Auftreten eines vordefinierten Ereignisses ermöglichen – aktuell relevante Zustandsänderungen auf dem Zielsystem im Experiment zu registrieren. Dieses Vorgehen wird durch den ListenerManager verwaltet, indem Schnittstellen für das Anlegen von EventListenern und Schnittstellen für die Erzeugung von zugehörigen Events angeboten werden. Bei Auftreten eines Ereignisses werden alle registrierten Listener, die der Ereignisklasse entsprechen, auf Übereinstimmung der Ereignisparameter geprüft und gegebenenfalls benachrichtigt. Nach aktuellem Stand sind folgende Ereignisarten definiert:

• Breakpoint: Soll die Ausführung einer bestimmten Instruktion (beispielsweise der Eintritt in die untersuchte Funktion) erkannt werden, so lässt sich ein Breakpoint-

2.6 Grundlagen

```

// Empfange Parameter von der Kampagne

jc.getParam(par);

3

// Lade vorher gespeicherten Zustand: Die Ausführung befindet

4

5

// sich nun am Eintritt der zu untersuchenden Funktion.

simulator.restore("sav/p_entry.sav");

7

8

// Breakpoint auf der zum Injektionszeitpunkt gehörenden

9 // dynamischen Instruktion

10 BPSingleListener ev_fi_instr;

11

ev_fi_instr.setWatchInstructionPointer(ANY_ADDR);

12 ev_fi_instr.setCounter(par.injection_instr());

simulator.addListenerAndResume(&ev_fi_instr);

13

14

15

// Injektion: Einzelner Bitfehler im spezifizierten Register

16 ConcreteCPU cpu = simulator.getCPU(0);

17 Register *r = cpu.getRegister(par.inject_register());

18 regdata_t regval = cpu.getRegisterContent(r);

19 cpu.setRegisterContent(r, regval ^ (1 << par.bitpos()));</pre>

20

21

// Nachuntersuchung: Traps, Zeitüberschreitung oder Terminierung?

22 TrapListener ev_trap;

23 simulator.addListener(&ev_trap);

24 // Zeitbedingung: Berechnung in unter 1000 Mikrosekunden

25 TimerListener ev_timeout(1000);

26 simulator.addListener(&ev_timeout);

27 BPSingleListener ev_func_end(ADDR_FUNC_END);

28

simulator.addListener(&ev_func_end);

29

// Warte auf Ereignis

30 BaseListener* ev = simulator.resume();

// Speichere Ergebnis im Parameter-Objekt

31

32 if (ev == &ev_func_end) {

33

unsigned char result;

34

result = simulator.getMemoryManager().getByte(ADDR_RESULT);

par.set_resulttype(LOG_NORMAL);

35

36

par.set_result(result);

37 } else if (ev == &ev_trap) {

38

par.set_resulttype(LOG_TRAP);

} else if (ev == &ev_timeout) {

40

par.set_resulttype(LOG_TIMEOUT);

41

}

42

43 // Kommuniziere Ergebnis zurück an Kampagnen-Verwaltung

jc.sendResult(par);

```

Abbildung 2.8: Beispielhafter Experimentcode, aktualisiert nach aktueller Schnittstelle aus [SHK+12]. Das Experiment fordert zunächst die Experimentparameter von der Kampagne an. Anschließend wird ein vorher gespeicherter Simulatorzustand geladen, um das Experiment zu initialisieren. Es wird mittels Breakpoint-Listener zum Injektionszeitpunkt navigiert, am Injektionsort ein Bitfehler injiziert und anschließend mittels Trap-, Timerund auf das Funktionsende konfiguriertem Breakpoint-Listener der Ausgang des Experiments bestimmt.

Ereignis registrieren. Ein Breakpoint ist durch die zu beobachtende Instruktionsadresse definiert. Bei der Registrierung wird automatisch die nötige Modifikation im Backend durchgeführt, um dieses Ereignis abfangen zu können. Es besteht ebenfalls die Möglichkeit, ein Intervall mehrerer Instruktionen zu beobachten, um beispielsweise einen durch Fehlerinjektion bedingten Einsprung in Datenbereiche des Speichers zu erkennen, die keinen Code enthalten.

- MemoryAccess: Wird ein durch Adresse, Länge und Art (lesend oder schreibend) definierter Speicherzugriff durchgeführt, so kann dies mittels eines MemoryAccess-Ereignisses angezeigt werden. Es wird somit möglich, beispielsweise einen Speicherzugriff zu erkennen, der aufgrund eines injizierten Fehlers in einen nicht erlaubten Bereich verläuft.

- **Trouble:** Ein sogenanntes Trouble-Ereignis definiert das Auftreten eines unvorhergesehenen Ereignisses auf dem Zielsystem. Konkrete Ausprägungen sind Ereignisse bei einem *Interrupt* oder *Trap*. Diese Ereignisse werden in Experimenten insbesondere für die Erkennung von durch Fehlerinjektion verursachten Traps verwendet.

- **IOPort:** Wird auf der Zielplattform eine Ein-/Ausgabe-Operation mittels Zugriff auf einen *I/O-Port* durchgeführt, so kann ein Ereignis erzeugt werden, um beispielsweise den Inhalt der Datenübertragung im Experiment auszulesen.

- Jump: Für die Registrierung von Sprüngen im Programmcode kann ein Jump-Ereignis herangezogen werden.

- Timer: Soll beispielsweise bei der Nachuntersuchung eines Fehlerinjektionsexperiments beobachtet werden, ob das Zielsystem innerhalb einer definierten Zeitspanne den Code nicht bis zum Ende ausführt, so kann dies mittels eines Timer-Ereignisses geprüft werden.

- Guest: Soll eine direkte Kommunikation von dem auf dem Zielsystem zur Kampagne realisiert werden, so kann dies mittels dieser Ereignisse realisiert werden. Es können Zeichenketten auf mehreren sogenannten *Ports* übertragen werden. Die Funktionalität der Ports dient hierbei der Realisierung mehrerer virtueller Kommunikationskanäle, so dass beispielsweise ein Kanal für Fehlermeldungen und ein Kanal für Status-Meldungen genutzt werden kann.

Zur Veranschaulichung der Verwendung der Ereignisschnittstelle kann der Beispielcode aus Abbildung 2.8 herangezogen werden. Hier wird beispielhaft ein an Abbildung 2.2 angelehntes einfaches Experiment definiert, welches die konkreten Experimentparameter von der Kampagne bezieht (eine detaillierte Betrachtung der Kampagnenverwaltung erfolgt in Abschnitt 2.6.2). Der Injektionszeitpunkt wird mittels eines Listeners für Breakpoint-Events realisiert, welcher bei jeder ausgeführten Instruktion aktiviert wird. Durch den Einsatz eines Zählers ist es somit möglich, eine definierte Anzahl ausgeführter Instruktionen abzuwarten. Der Injektionszeitpunkt ist demnach direkt durch seine Position im Trace definiert. Anschließend wird ein einzelner Bitfehler in ein CPU-Register

2.6 Grundlagen

injiziert. Zu diesem Zweck wird das Register ausgelesen, das entsprechende Bit invertiert und anschließend wird das Register erneut geschrieben.

Ereignisse sind insbesondere für die Nachuntersuchung von hoher Bedeutung. So ist zu erkennen, dass die konkrete Nachuntersuchung die drei Fälle der korrekten Abarbeitung des Funktionscodes, einer Zeitüberschreitung oder eines ausgelösten Traps unterscheidet. Zu diesem Zweck werden in dem Beispiel TrapListener, TimerListener und BPSingleListener registriert. Nach Signalisierung eines Ereignisses wird geprüft, um welches Ereignis es sich handelt und mit dieser Information wird das Ergebnis des Experiments zurückgegeben.

Die Verwendung einer ereignisbasierten Schnittstelle ist insbesondere wichtig, da die Experimentdurchführung in Fail\* mithilfe sogenannter Koroutinen, also kooperativer Programmfäden, erfolgt [Con63]. Dieses Verfahren wird verwendet, damit zu jedem Zeitpunkt immer nur entweder die Ausführung des Zielsystems oder der Experimentcode aktiv ist. Hierdurch wird sichergestellt, dass alle relevanten Informationen im Experiment signalisiert werden. Der Ablauf sieht demnach vor, dass das Experiment zunächst nötige Modifikationen durchführt und Ereignis-Listener registriert, um anschließend aktiv den Kontrollfluss an das Zielsystem abzugeben, welches seinerseits wiederum solange läuft, bis ein relevantes Ereignis aufgetreten ist und an Fail\* signalisiert wird. In diesem Fall wird ein Koroutinenwechsel ausgelöst, wodurch der Kontrollfluss der Koroutine des Experiments forgeführt wird. Kontrollflusswechsel werden demnach experimentseitig mittels simulator.resume() (s. Abbildung 2.8) und Backend-seitig durch Auslösung von Ereignissen aktiviert.

Der aktive Zugriff auf Komponenten des Backends erfolgt durch Verwendung der Schnittstellen des SimulatorControllers. Hier wird nach Art der zugegriffenen Komponente eine Unterteilung in MemoryManager und abstrakte CPU durchgeführt. Diese Komponenten liefern Meta-Informationen über die verwaltete Komponente, um eine generische Fehlerinjektion zu ermöglichen. So bietet die abstrakte CPU beispielsweise einen Iterator über alle Prozessor-Register und der MemoryManager gibt Informationen zu Größe und Ort des genutzten Speichers an. Des Weiteren definiert der SimulatorController Schnittstellen, um einen Neustart durchzuführen und einen vorher gespeicherten Systemzustand wiederherzustellen (s. Abb. 2.8).

### 2.6.2 Kampagnenverwaltung

Aufgrund der in Abbildung 2.6 schematisierten verteilten Architektur von Fail\* wird eine zentrale Verwaltung für Kampagnen ausgeführt, welche Zugriff auf eine SQL-Datenbank mit Experiment-Parametern und -Ergebnissen hat. Um die Möglichkeit zu erhalten, mehrere Kampagnen für verschiedene Benchmarks und deren Varianten als Zielapplikationen durchführen zu können, kann eine Datenbank mehrere Kampagnen mittels der Verwendung entsprechender Identifizierer verwalten. Für die Übertragung der Experiment-Parameter kann ein vorkonfigurierter Nachrichtentyp verwendet werden, sodass eine vorgegebene Kampagnenimplementierung vom Benutzer verwendet werden kann. Alternativ können allerdings auch spezialisierte Nachrichtenformate verwendet werden, die jedoch eine Implementierung zugehörigen Kampagnencodes bedingen. Experimen-

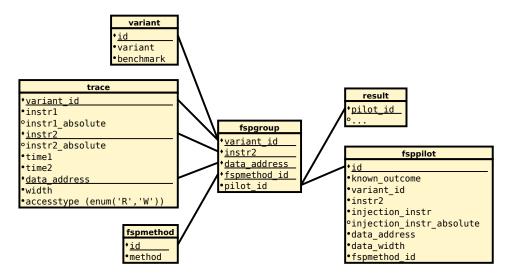

Abbildung 2.9: Darstellung der von Fail\* verwendeten Datenbankstruktur.

tergebnisse werden mittels eines weiteren individuell anzulegenden Nachrichtenformat übertragen, dessen Felder direkt in eine Ergebnistabelle geschrieben werden. Die Einzelschritte werden im Folgenden detaillierter betrachtet.

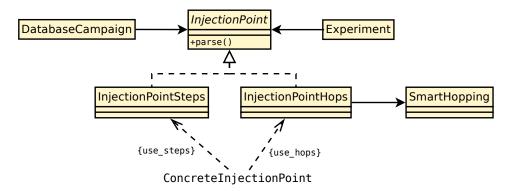

Grundlage eines Experiments bildet der Programm-Trace. Dieser wird initial und vor Durchführung der Kampagne aufgezeichnet. In Abschnitt 2.5 wurde gezeigt, dass eine vollständige Abdeckung des Fehlerraums mit Experimenten im Allgemeinen nicht sinnvoll ist, da sich durch das Def-Use-Schema für die Injektion in Speicherzellen oder Register Äquivalenzklassen mit gleichen Ergebnissen bilden. Um demnach initial die Parameter-Tabelle zu füllen, werden die Äquivalenzklassen mittels des sogenannten Prunings bestimmt. Werden im Folgenden Experiment-Parameter an die Fail\*-Instanzen verteilt, so genügt für die Injektion in ein Speicherwort der Adresse x die Übertragung eines innerhalb der zugehörigen Äquivalenzklasse  $A_x^{(y)}$  befindlichen Injektionszeitpunktes. Dies gilt, da a priori bekannt ist, dass die Injektionsergebnisse aller Elemente der Klasse gleich sind. Da bei Verwendung von Fail\* grundlegend von der Verwendung des Pruning ausgegangen wird, geschieht die Reduktion der Experimentmenge direkt beim Import des Traces in die Datenbank. Somit lässt sich der Speicheraufwand der Datenbank potenziell drastisch reduzieren, ohne notwendige Informationen zu verlieren.

Die Kommunikation zwischen Kampagnenverwaltung und Fail\*-Instanzen wird mittels Google Protocol Buffers (Protobuf) [Goo13] durchgeführt. Es handelt sich hierbei um ein leichtgewichtiges Datenübertragungsformat [GDK11], welches sich insbesondere dazu eignet, Nachrichten in eine automatisch aus dem Nachrichtenformat generierte Datenbanktabelle zu transferieren. In Fail\* werden Protobuf-Nachrichten für die Kontrollkommunikation zwischen Client und Server (Parameter-Anfrage/-Antwort) und für die Übertragung der Parameter und der Experimentergebnisse verwendet. Da das Ergebnis-Nachrichtenformat individuell für eine Kampagne angepasst werden kann, wird die Ergebnistabelle automatisch aus diesem Format generiert.

2.6 Grundlagen

Die in Fail\* verwendete Struktur von Datenbanktabellen wird in Abbildung 2.9 schematisiert. Die Aufgaben der verschiedenen Tabellen werden im Folgenden kurz erläutert:

- Die Tabelle variant wird verwendet, um mehrere Benchmark-Varianten und verschiedene darin eingebrachte Fehlertoleranzverfahren zu untersuchen. Alle verwendeten Tupel von variant und benchmark erhalten durch diese Tabelle einen eindeutigen Identifizierer und bei der anschließenden Untersuchung können die Ergebnisse in Relation zu der jeweiligen Variante gesetzt werden. Die Spalten variant und benchmark enthalten jeweils textuelle Beschreibungen.

- Für jede Variante werden in der Tabelle trace die durch Fault-Space-Pruning bestimmten Äquivalenzklassen eingetragen, welche durch ihre Anfangs- und Endpunkte definiert sind. Hierbei ist zu beachten, dass nach Notation aus Abschnitt 2.5 der Anfangspunkt dem Zeitpunkt  $t_l+1$  entspricht, da der vorangegangene Speicherzugriff nicht zur Äquivalenzklasse gehört. Die Äquivalenzklassen werden sowohl durch Trace-Positionen (instr1, instr2), als auch durch Zeiten in der Ausführung (time1, time2) repräsentiert. Der Unterschied liegt hier darin, dass unterschiedliche Instruktionen im Allgemeinen unterschiedliche Ausführungsdauern aufweisen. Es ist daher durch den Einsatz der Definition mit (time1, time2) möglich, Ergebniswerte in eine zeitliche Relation bezüglich der Gesamtausführung des Zielsystems zu setzen, wobei die Werte (instr1, instr2) nur Aufschluss über die Anzahl der betroffenen Instruktionen geben. Mithilfe der Einträge für Instruktionsadressen der unteren und oberen Begrenzung der Äquivalenzklasse wird es zusätzlich ermöglicht, zu prüfen ob sich das Zielsystem zum Injektionszeitpunkt tatsächlich an der richtigen Instruktion befindet. Weiterhin beschreibt jeder Eintrag der Tabelle trace die Art des Speicherzugriffs, definiert durch Adresse (data address), Breite (width) und Zugriffsart (accesstype).

- In der Tabelle fsppilot werden Einträge der Tabelle trace zu sogenannten Experiment-Piloten zusammengefasst. Hier werden die Parameter für alle einer Kampagne zugehörigen Experimente angelegt. Ein Pilot bietet die Möglichkeit, Pruning auch auf anderen Ebenen als dem in dieser Arbeit beschriebenen Def-Use-Schema durchzuführen. Dies wird über den Eintrag fspmethod\_id angezeigt. Da Mengen von Experimenten existieren, für die bereits a priori das Ergebnis des Experiments bekannt ist, werden sie durch den Wahrheitswert known\_outcome markiert. Ein Pilot enthält die Parameter injection\_instr, data\_address und data\_width unter denen das zugehörige Experiment gesteuert wird.

- Zur Realisierung verschiedener Pruning-Methoden ordnet die Tabelle fspmethod jedem Eintrag aus fsppilot eine textuelle Beschreibung der Art der Zusammenfassung von Experimenten zu.

- Zu jedem Eintrag der Tabelle *fsppilot* werden je nach Fehlermodell ein oder mehrere Einträge in der Tabelle *result* angelegt. Im Diagramm ist angedeutet, dass nur die Verbindung zur Tabelle *fsppilot* mithilfe des entsprechenden Identifizierers fest

definiert ist. Alle weiteren Einträge der Ergebnistabelle sind experimentabhängig. Die Definition der Tabellenspalten wird automatisch aus dem für eine Kampagne definierten Ergebnisnachrichtenformat generiert.

• Die Tabelle fspgroup bietet schließlich die Möglichkeit zur Verknüpfung der verschiedenen Tabellen, um im Anschluss an die Durchführung einer Kampagne entsprechende Nachuntersuchungen auf den Daten durchführen zu können. Sie ordnet den Identifizierern variant\_id, instr2, data\_address und fspmethod\_id einem Eintrag aus fsppilot und damit einem Eintrag der Ergebnistabelle zu.

Durch diese Datenbank-Architektur ist eine Erweiterbarkeit hinsichtlich verschiedener Ergebnistypen und Pruning-Methoden möglich. Es können in einer Kampagne verschiedene Benchmark- und Fehlertoleranz-Varianten untersucht werden. Außerdem wird eine anschließende Auswertung der Ergebnisse durch den Zusammenschluss der generierten Daten möglich.

### 2.7 Zusammenfassung

In diesem Kapitel wurden die Grundlagen dieser Arbeit erläutert. Es wurde zunächst auf grundlegende Begrifflichkeiten in Bezug auf Fehlerinjektion eingegangen, auf denen im Folgenden aufgebaut wird. Es wurde gezeigt, dass Hardware-Fehler durch verschiedene Modelle beschreibbar sind, wobei das im Kontext der Arbeit entworfene Fehlerinjektionssystem keine Einschränkung auf ein konkretes Modell vorsieht. Des Weiteren wurden Zuverlässigkeitsmetriken vorgestellt, welche den Vergleich von verschiedenen Fehlertoleranzverfahren auf Basis der Ergebnisse von Fehlerinjektion erlauben. Es wurden die Software-, Hardware-, Simulator- und OCD-basierten Fehlerinjektionsverfahren einander vergleichend gegenübergestellt, wobei im Folgenden auf den Erkenntnissen bezüglich der OCD-basierten Verfahren aufgebaut wird. Bei der Entwicklung von FailPanda wird die in diesem Kapitel vorgestellte Optimierung von Fehlerinjektionsexperimenten angewandt, um die durchzuführende Experimentmenge zu reduzieren. Schließlich wurde in diesem Kapitel detailliert auf das Fehlerinjektions-Framework Fail\* eingegangen. Die Anbindung eines eingebetteten Systems an dieses Framework zur Durchführung von OCD-basierter Fehlerinjektion wird in den nachfolgenden Kapiteln erläutert.

## 3 Analyse und Entwurf

Dieses Kapitel beschreibt konkrete Entwurfsentscheidungen bei der Entwicklung eines Fehlerinjektionssystems auf Basis von COTS-Hardware. Die Entwurfsentscheidungen werden auf Basis einer Anforderungsanalyse begründet und es werden Alternativen diskutiert. Im vorangegangenen Kapitel, insbesondere in den Abschnitten 2.4.4 und 2.6, wurden bereits wichtige Anforderungen an die Anbindung eines Hardwaresystems an ein Fehlerinjektionssystem, schwerpunktmäßig in Bezug auf Fail\*, beschrieben. Auf dieser Grundlage werden in Abschnitt 3.1 zunächst wichtige Anforderungen an das System hinsichtlich Funktion und Performanz identifiziert. Darauf basierend wird in einem Top-Down Verfahren in Abschnitt 3.2 zunächst der Entwurf der konkreten Gesamtlösung erläutert, um anschließend in den Abschnitten 3.3 bis 3.7 auf den Entwurf der Einzelfunktionalitäten einzugehen.

### 3.1 Anforderungsanalyse

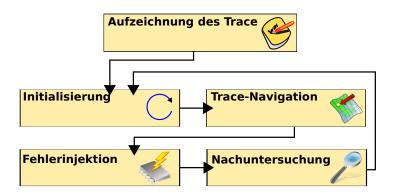

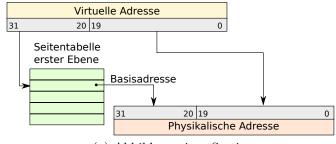

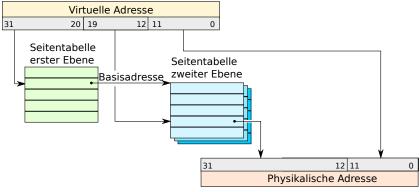

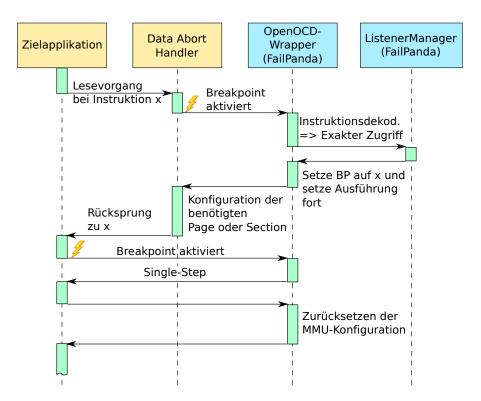

Die im vorherigen Kapitel beschriebenen Funktionen, insbesondere bezüglich OCD-basierter Fehlerinjektion, werden in diesem Kapitel als funktionale Grundanforderungen interpretiert, sodass ein auf diesen Anforderungen basierender Entwurf des Gesamtsystems durchgeführt werden kann. Abbildung 3.1 zeigt die nach den Phasen Trace-Aufzeichnung, Initialisierung, Trace-Navigation, Fehlerinjektion und Nachuntersuchung getrennten verschiedenen Aufgaben eines Fehlerinjektionssystems. Im Folgenden werden die Anforderungen an diese Einzelfunktionen in der aufgezeichneten Reihenfolge analysiert.

Abbildung 3.1: Schematische Aufteilung von Fehlerinjektionsexperimenten in 5 Phasen und ihre Ablaufreihenfolge für die Durchführung einer Kampagne.