## Bachelorarbeit

Erweiterung des ereignisbasierten Betriebssystems CyPhOS um eine dynamische cache-gewahre Speicherverwaltung

Christian Hakert 28. Juli 2017

Betreuer:

Prof. Dr.-Ing. Olaf Spinczyk M.Sc. Hendrik Borghorst

Technische Universität Dortmund Fakultät für Informatik Lehrstuhl 12 Arbeitsgruppe Eingebettete Systemsoftware http://ess.cs.tu-dortmund.de

#### Zusammenfassung

Moderne cyber-physikalische Anwendungen stellen hohe Anforderungen an ihre Ausführungsplattform. Neben harten Echtzeitanforderungen setzen solche Anwendungen auch häufig eine dynamische Ressourcenverwaltung voraus. Programme sollen z.B. während ihrer Ausführung um Funktionalitäten oder sogar um weitere Programminstanzen erweitert werden können. Ein weiteres Ziel ist es, diesen Anforderungen nicht nur mit spezieller, sondern auch mit möglichst günstiger general-purpose Hardware gerecht zu werden. Das Betriebssystem CyPhOS bietet Anwendungen eine Umgebung, um diese mit harten Echtzeitanforderungen auf moderner general-purpose Hardware auszuführen. Diese Arbeit erweitert CyPhOS um eine dynamische Speicherverwaltung, sodass auch die Anforderungen an die dynamische Ressourcennutzung während der Ausführung der Programme im Bezug auf Speicher erfüllt werden können.

## Inhaltsverzeichnis

| 1. | Einl | leitung                                          | ]       |

|----|------|--------------------------------------------------|---------|

| 2. | 2.1. | leitung zum Betriebssystem CyPhOS  Komponenten   | 6       |

| 3. | Das  | Speichermodell von CyPhOS                        | Ę       |

| 4. | Gru  | ndlegende Konzepte der Speicherverwaltung        | ,       |

|    | 4.1. | Speicherabhängigkeiten und Synchronisierung      | ,       |

|    | 4.2. | Speicherklassen                                  | 8       |

|    |      | 4.2.1. Immer im Cache (fully cached)             | 6       |

|    |      | 4.2.2. Dynamisch-gecachet (dynamic cached)       | )       |

|    |      | 4.2.3. Nicht-gecachet (not cached)               | (       |

|    | 4.3. | Micro-Heaps und Component-Heaps                  | 10      |

|    | 4.4. | Freispeicherverwaltung                           | 1       |

|    | 4.5. | Schnittstelle                                    | 1:      |

| 5. | Imp  | lementierung                                     | 1       |

|    | _    | Anlegen der Speicherpools                        | 1!      |

|    | 5.2. |                                                  | 1!      |

|    | 5.3. | Freispeicherverwaltung                           | 18      |

|    |      | 5.3.1. Belegung von Speicher                     | 18      |

|    |      | 5.3.2. Freigabe von Speicher                     | 19      |

|    | 5.4. |                                                  | 20      |

|    | 5.5. | Dynamisch gecachete Speicher (Access-Flag)       | 2       |

|    |      | 5.5.1. Aktivieren des Access-Flag                | 2       |

|    |      | 5.5.2. Nutzung des Access-Flag                   | 25      |

|    |      | 5.5.3. Behandlung des Access-Flag-fault          | 22      |

|    | 5.6. | Nicht gecacheter Speicher                        | 2       |

|    | 5.7. | new-Operator                                     | 2       |

|    | 5.8. | Speicherabhängigkeiten                           | $2^{2}$ |

|    |      | 5.8.1. Kohärenz im Translation-Look-Aside-Buffer | 2!      |

| 6. | Anv  | vendungsbeispiel: CAN-Bus                        | 27      |

|    |      | Der CAN-Treiber                                  | 2'      |

|    |      |                                                  |         |

|    | 6.2.                                 | Anwendungskomponente: Gangwahlschalter                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                             |

|----|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 7. | 7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5. | Konstruierte Testumgebung Auswertung der Messungen Zugriffszeiten in den verschiedenen Speicherklassen Zugriffszeiten unter parallel stattfindenden Zugriffen 7.4.1. Keine Verdrängungen im Cache 7.4.2. Verdrängungen im Cache Vergleich mit reinem Hardware-Cache-Management 7.5.1. Kein paralleler Betrieb (vgl. Kapitel 7.3) 7.5.2. Paralleler Betrieb (vgl. Kapitel 7.4) Verhalten der Vorladezeiten der Komponenten Fazit der Evaluation | 29<br>30<br>31<br>34<br>34<br>38<br>42<br>42<br>46<br>48<br>51 |

| 8. |                                      | Stand der Forschung                                                                                                                                                                                                                                                                                                                                                                                                                            | 53<br>53<br>53<br>54<br>54<br>54                               |

|    |                                      | 8.4.2. Alignment an Cache-Grenzen                                                                                                                                                                                                                                                                                                                                                                                                              | 55<br>55                                                       |

| Li | terat                                | urverzeichnis                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57                                                             |

| Al | obild                                | ungsverzeichnis                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                             |

| Α. | A.1.<br>A.2.                         | Zugriffszeiten ohne Störungen  Zugriffszeiten unter Störungen  A.2.1. Keine Verdrängungen  A.2.2. Verdrängungen  Hardware-Cache-Verwaltung                                                                                                                                                                                                                                                                                                     | I<br>I<br>I<br>II<br>II                                        |

| В. | B.1.<br>B.2.                         | riffszeitmessungen auf einem Wandboard mit i.MX6 CPU Speicherzugriffe ohne Störung                                                                                                                                                                                                                                                                                                                                                             | V VII VIII XI XIV XIV XVII                                     |

| <ul><li>B.4. Verhalten der Vorladezeiten der Komponenten</li><li>B.5. Fazit der Evaluation</li></ul> |     |       |

|------------------------------------------------------------------------------------------------------|-----|-------|

| C. Statistische Kennzahlen der Evaluationsergebnisse auf ei                                          | nem |       |

| Wandboard (Anhang B)                                                                                 |     | XXIII |

| C.1. Zugriffszeiten ohne Störungen                                                                   |     | XXIII |

| C.2. Zugriffszeiten unter Störungen                                                                  |     |       |

| C.2.1. Keine Verdrängungen                                                                           |     |       |

| C.2.2. Verdrängungen                                                                                 |     |       |

| C.3. Hardware-Cache-Verwaltung                                                                       |     |       |

## 1. Einleitung

CyPhOS ist ein Betriebssystem, das ein Echtzeitverhalten auf moderner Hardware ermöglichen soll [7]. Um dies zu erreichen, benötigt das Betriebssystem eine Möglichkeit, Inhalte gezielt in Cache-Ways laden zu können und diese vor der Verdrängung zu schützen. Der CoreLink Level 2 Cache-Controller L2C-310 bietet die Möglichkeit einzelne Cache-Ways des L2-Caches zu sperren [2]. Dieser Controller kommt in Cortex-A9 Prozessoren zum Einsatz [4]. Wird ein Cache-Way gesperrt, so können Inhalte nicht mehr aus diesem verdrängt werden. Es können auch keinen neuen Inhalte in den gesperrten Cache-Way abgelegt werden. CyPhOS implementiert auf dieser Basis eine Software-Cache-Verwaltung, mit der Inhalte gezielt in einen Cache-Way geladen werden können und dieser anschließend gesperrt werden kann. Somit kann sichergestellt werden, dass ein bestimmter Inhalt garantiert im L2-Cache liegt.

Das Betriebssystem CyPhOS ist größtenteils in C++ geschrieben, bietet aber keine Möglichkeiten, zur Laufzeit Speicher zu allozieren oder Objekte zu erstellen. Daher wird CyPhOS in dieser Arbeit um eine dynamische Speicherverwaltung erweitert. Damit soll es Anwendungen ermöglicht werden, zur Laufzeit Speicher für individuelle Verwendungszwecke zu allozieren und auch wieder freigeben zu können. Dadurch soll den Anwendungen ein breiteres Spektrum an Möglichkeiten geboten werden, wie sie z. B. im Kontext der cyber-physikalischen Systeme benötigt werden. Weiterhin soll die Speicherverwaltung das dynamische Erstellen und Vernichten von Objekten ermöglichen. Dadurch können Programme ihre Funktionalitäten erweitern oder das Betriebssystem kann Programme generieren, die anschließend zur Ausführung kommen.

Damit auch für die Speicherverwaltung und vor allem für die allozierten Speicherbereiche dieselben Echtzeitanforderungen erfüllt werden können, wie CyPhOS sie für die Anwendungen bereits erfüllt, muss die Speicherverwaltung ebenfalls eine aktive Cache-Verwaltung durchführen. Für allozierte Speicher muss dieselbe Cache-Gewahrheit sichergestellt werden können, wie für Anwendungen selber. Dies erfordert eine Interaktion zwischen der Speicherverwaltung und den Betriebssystemfunktionen, weshalb die Speicherverwaltung in das Betriebssystem selber integriert wird.

## 2. Einleitung zum Betriebssystem CyPhOS

CyPhOS (Cyber-physical operating system) ist ein Echtzeitbetriebssystem für moderne Mehrkern-Hardware. Dabei wird die Annahme zu Grunde gelegt, dass die parallele Nutzung geteilter Ressourcen durch mehrere Prozessorkerne der Hauptgrund für unvorhersagbare Laufzeiten ist. Während der Ausführung eines Programms auf einem Mehrkern-Prozessor ist der gemeinsame Bus zum Hauptspeicher u. a. eine gemeinsam genutzte Ressource [7]. CyPhOS stellt sicher, dass während der Ausführung des Betriebssystems keine Zugriffe in den Hauptspeicher erfolgen und somit die gemeinsame Nutzung dieser Ressource vermieden wird. Um Hauptspeicherzugriffe zu vermeiden führt CyPhOS eine aktive Cache-Verwaltung durch. Diese sorgt dafür, dass jeglicher Programmcode und jegliche Programmdaten, die zur Ausführung kommen, vorher in den L2-Cache geladen wurden. Um dies zu erreichen, stellt CyPhOS eine Abstraktion für Anwendungsprogramme zur Verfügung.

## 2.1. Komponenten

Jedes Anwendungsprogramm, welches für CyPhOS entwickelt wird, ist eine Komponente. Die Komponente besteht lediglich aus dem Daten- und Text-Segment des kompilierten Programmcode. Wird die Komponente ausgeführt, so wird ihr ein Stack aus einem zentralen Pool zugewiesen. Eine Komponente kann verschiedene Einstiegspunkte haben, an denen sie zur Ausführung kommt. Beim Kompilieren und Linken des Betriebssystems werden die Komponenten auf eine bestimmte Art angeordnet. Dadurch ist es möglich, eine einzelne Komponente in einen Cache-Way zu laden und sicherzustellen, dass ihre Ausführung keine Hauptspeicherzugriffe benötigt.

## 2.2. Events und Trigger

Wenn eine Komponente ausgeführt werden soll, muss CyPhOS diese zuerst in den Cache laden, falls dies nicht schon zu einem früheren Zeitpunkt geschehen ist und die Komponente nicht wieder aus dem Cache verdrängt wurde. Dies hat zur Folge, dass das Betriebssystem für jede Ausführung einer Komponente benachrichtigt werden muss. Um dies zu gewährleisten führt CyPhOS eine Abstraktion zum Ausführen von Komponenten ein. Eine Funktion der Komponente kann nicht aus einer anderen heraus angesprungen werden. Anstatt dessen muss ein Event ausgelöst werden. Für ein Event ist ein Trigger hinterlegt, der in Folge des Events ausgeführt werden soll. Zu dem Trigger gehört unter anderem eine Funktion einer Komponente, die ausgeführt werden soll. Trigger stellen die Einstiegspunkte in eine Komponente dar.

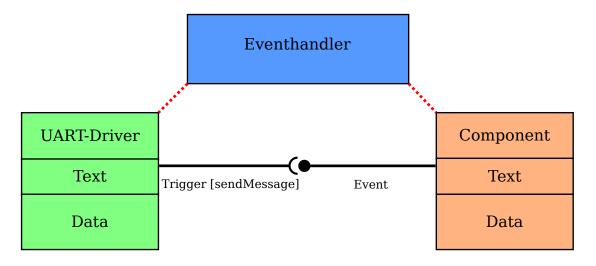

Abbildung 2.1.: Interaktion zwischen zwei Komponenten

Der UART Treiber stellt einen Trigger zur Verfügung, um eine Nachricht abzusenden. Die Komponente muss ein Event auslösen, um diese Funktion nutzen zu können. Logisch interagiert die Komponente direkt mit dem Treiber, tatsächlich erfolgt die Auslösung des Trigger aber durch den Eventhandler.

Um ein Event auszulösen, muss eine Komponente den Eventhandler benachrichtigen. Dieser kann daraufhin überprüfen, ob die Zielkomponente bereits im Cache liegt, diese eventuell laden und den zugehörigen Trigger zur Ausführung bringen.

# 3. Das Speichermodell von CyPhOS

Ein zentrales Merkmal von CyPhOS ist die aktive Cache-Verwaltung. Damit Komponenten gezielt in den L2-Cache geladen werden können, werden diese beim Linken des Betriebssystems auf eine bestimmte Art angeordnet.

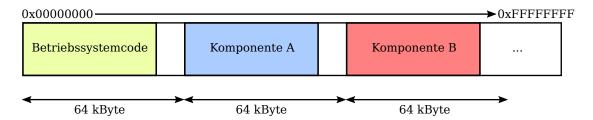

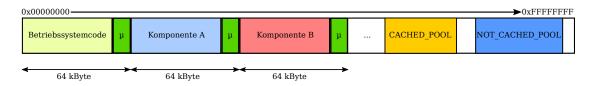

Abbildung 3.1.: Hauptspeicherabbild von CyPhOS mit zwei Komponenten

Wie in Abbildung 3.1 zu erkennen ist, werden alle Betriebssystemfunktionen an den Anfang des Hauptspeichers platziert. Dazu gehören u. a. das Eventhandling und die Cache-Verwaltung. Anschließend folgt der kompilierte Code aller Komponenten. Dieser besteht jeweils aus dem Text und Daten-Segment. Jede Komponenten wird an eine 64kB Grenze ausgerichtet. Jeder Cache-Way des Prozessors hat eine Größe von 64kB, somit ist gewährleistet, dass jede Komponente in einen separaten Cache-Way geladen werden kann und aufgrund der Cache-Assoziativität keine Überschneidungen auftreten.

Während des Startvorgangs des Betriebssystems CyPhOS wird der L2-Cache initialisiert und alle Cache-Ways werden gesperrt. Der Cache-Controller kann nur ungesperrte Cache-Ways verwenden, um Inhalte abzulegen. Aus gesperrten Cache-Ways werden Inhalte niemals verdrängt. Wenn eine Komponente in den Cache geladen werden soll, wird ein Cache-Way entsperrt und Preload-Instruktionen für den gesamten Speicher der Komponente aufgerufen. Der Cache-Controller legt dann die Komponente gezwungenermaßen in den entsperrten Cache-Way. Anschließend wird der Cache-Way wieder gesperrt und das Laden der Komponente ist abgeschlossen.

Während ein Cache-Way entsperrt ist, muss sichergestellt werden, dass kein anderer Kern Zugriffe auf nicht gecacheten, cachebaren Speicher ausführt. Dadurch würde der Cache-Controller eben auch die zugegriffenen Inhalte in dem entsperrten

Cache-Way platzieren. Zum einen wird so ein paralleler Zugriff dadurch verhindert, dass immer nur eine Komponente zeitgleich vorgeladen wird. Zum anderen erfolgen nirgendwo im Betriebssystem Zugriffe auf Inhalte die nicht im Cache liegen.

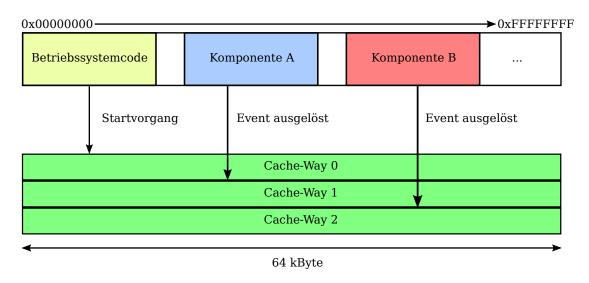

Während des Startvorgangs des Betriebssystems wird der Systemcode in einen Cache-Way geladen und dieser anschließend für jegliche weitere Verwendung gesperrt. Wird ein Event ausgelöst, welches einen Trigger startet, der eine nicht geladene Komponente zur Ausführung bringt, so wird diese Komponente vor der Ausführung des Trigger in einen freien Cache-Way geladen. Dieses Verhalten wird in Abbildung 3.2 veranschaulicht.

Abbildung 3.2.: Laden der Komponenten in den L2-Cache

# 4. Grundlegende Konzepte der Speicherverwaltung

Die Speicherverwaltung, die für CyPhOS entwickelt werden soll, muss die Cache-Gewahrheit des Systems sicherstellen. Dies bedeutet, dass sichergestellt werden muss, dass Zugriffe in reservierten Speicher keine Hauptspeicherzugriffe verursachen, sondern lediglich auf den L2-Cache zugreifen. Weiterhin soll die Speicherverwaltung dynamisch betrieben werden. Komponenten sollen zur Laufzeit Speicher reservieren und freigeben können. Sowohl logisch, als auch physikalisch werden reservierte Speicherbereiche der reservierenden Komponente zugeordnet. Somit können diese gemeinsam mit der Komponente vorgeladen werden. Dem Betriebssystem stehen nur eine stark begrenzte Anzahl von Cache-Ways zur Verfügung. Durch die Zuordnung der Speicherbereiche zu den Komponenten wird erreicht, dass der L2-Cache nur von den aktuell ausgeführten Komponenten und ihrem reservierten Speicher belegt wird.

## 4.1. Speicherabhängigkeiten und Synchronisierung

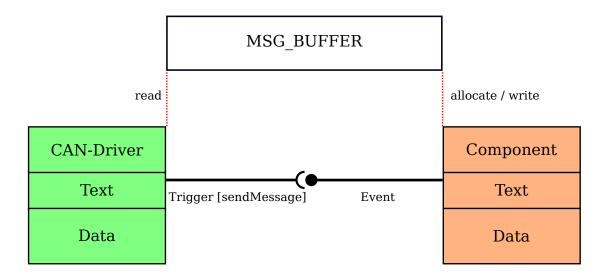

Die Speicherverwaltung soll ermöglichen, dass reservierter Speicher von verschiedenen Komponenten genutzt werden kann. Ein Anwendungsbeispiel dazu ist in Abbildung 4.1 dargestellt.

Hierbei muss die Cache-Gewahrheit ebenfalls sichergestellt werden. Um dies zu gewährleisten, kann eine Anwendungskomponente für jeden beliebigen Trigger Speicherabhängigkeiten angeben. Diese Abhängigkeiten werden von dem Eventhandler vor der Ausführung des Trigger überprüft und die entsprechenden Speicherbereiche in den Cache geladen. Zusätzlich findet im Eventhandler noch eine Synchronisierung statt. Es wird sichergestellt, dass niemals mehrere Komponenten gleichzeitig ausgeführt werden, die den selben Speicherbereich benötigen. Speicherabhängigkeiten können zur Laufzeit von jeder Komponente für jeden Trigger und für jeden reservierten Speicherabschnitt hinzugefügt und entfernt werden.

Abbildung 4.1.: Gemeinsam genutzter Speicher

Das Beispiel zeigt eine Komponente, die eine Nachricht über den CAN-Bus versendet. Der Treiber für den CAN-Bus stellt den Trigger "sendMessage" zur Verfügung. Die Komponente bereitet die zu versendende Nachricht in einem reservierten Speicherbereich vor. Der CAN-Treiber liest diesen Speicherbereich während der Ausführung des Trigger und versendet die Nachricht. Die Komponente kann eine Abhängigkeit für den Trigger "sendMessage" des CAN-Treibers hinzufügen, sodass die vorbereitete Nachricht garantiert im Cache liegt, wenn dieser Trigger zur Ausführung kommt. Das Schema lässt sich auch mit beliebig vielen Komponenten anwenden.

## 4.2. Speicherklassen

Die Anforderung an die Cache-Gewahrheit der Speicherverwaltung bringt starke Einschränkungen mit sich. Um den Anwendungen eine flexiblere und uneingeschränktere Speicherverwaltung anzubieten, werden drei verschiedene Speicherklassen implementiert, die unterschiedliche Grade der Cache-Gewahrheit erreichen.

## 4.2.1. Immer im Cache (fully cached)

Speicherbereiche, die in dieser Klasse reserviert werden, werden immer zusammen mit der Komponente in den L2-Cache geladen. Der Eventhandler überprüft vor der Ausführung eines Trigger die eingetragenen Speicherabhängigkeiten. Anschließend wird die Komponente selbst, aber auch die Speicherbereiche, die für diesen Trigger eingetragen sind, in einen freien Cache-Way geladen. In dieser Speicherklasse wird

sichergestellt, dass die reservierten Speicherbereiche bei der Ausführung der Komponente bereits im L2-Cache liegen. Der Nachteil ergibt sich aus der begrenzten Anzahl der Cache-Ways und der beschränkten Cache-Way Größe. Somit können für einen Trigger nur wenige und kleine Speicherbereiche aus dieser Klasse genutzt werden. Die Zugriffszeiten für Speicher aus dieser Klasse wiederum sind maximal gering und vorhersagbar. Die reservierten Speicherbereiche aus dieser Klasse verhalten sich identisch wie der Programmcode und die Programmdaten der Komponente selbst.

## 4.2.2. Dynamisch-gecachet (dynamic cached)

Die zweite Speicherklasse soll die Einschränkungen der ersten Speicherklasse aufweichen, ohne größere Nachteile mit sich zu bringen. Eine Anwendung kann in dieser Speicherklasse beliebig viel Speicher reservieren. Kommt ein Trigger zur Ausführung, so wird vorerst keiner der reservierten Bereiche geladen. Dies geschieht erst beim ersten Zugriff in einen reservierten Speicherbereich. Daraufhin wird der entsprechende Block in einen freien Cache-Way geladen. Alle weiteren reservierten Speicherbereiche dieser Klasse bleiben unangetastet. Für den ersten Zugriff auf einen Speicherbereich ergeben sich dadurch höhere Zugriffszeiten, alle weiteren Zugriffe sind dann allerdings ebenso schnell und vorhersagbar wie Zugriffe auf Speicher der ersten Klasse. Ein lokales Speicherverhalten der ausgeführten Anwendungen kommt den Zugriffszeiten zusätzlich zu Gute, denn ein Speicherbereich, der in den Cache geladen wurde, wird erst verdrängt, wenn der Cache-Way für andere Komponenten oder Speicherbereiche benötigt wird.

Für die Anwendungsentwicklung ergibt sich bei der Verwendung dieser Speicherklasse der Nachteil, dass eine statische Analyse des Programmverhaltens nicht mehr möglich ist. Insbesondere kann keine statische Überprüfung stattfinden, ob die zugegriffenen Inhalte in den Cache geladen werden können.

## 4.2.3. Nicht-gecachet (not cached)

Zuletzt wird Anwendungen noch die Möglichkeit geboten, Speicher zu reservieren, der niemals in den Cache geladen wird. Die Zugriffszeiten für diese Speicherklasse sind relativ hoch und unvorhersagbar. Es können allerdings nahezu beliebig große Speicherbereiche reserviert und genutzt werden, die nur durch die konfigurierbare Größe des Pool für nicht-gecachete Inhalte begrenzt sind. Die Verwendung dieser Speicherklasse ist besonders im Kontext der Mixed-Criticality Systeme sinnvoll. Dabei kann es z.B. von Interesse sein Messdaten in großem Rahmen abzuspeichern und Optimierungen mithilfe dieser Daten zu berechnen. Diese Aufgabe kann ein separater Prozessorkern übernehmen. Die Messdaten können in einem nichtgecacheten Speicherbereich abgelegt werden und die Optimierung würde somit die

zeitlichen Eigenschaften der anderen parallel laufenden Programme nicht beeinflussen.

## 4.3. Micro-Heaps und Component-Heaps

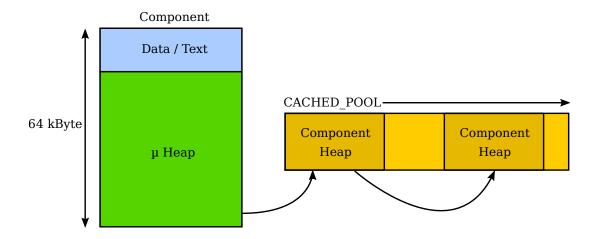

Damit die Leistungsfähigkeit der Speicherverwaltung erhöht wird, muss der reservierte Speicher möglichst fragmentierungsfrei platziert werden, damit beim Laden möglichst wenige Cache-Ways benötigt werden. In Abbildung 3.1 ist zu erkennen, dass einiger Speicherplatz bisher ungenutzt verbleibt. Aufgrund der Ausrichtung der Komponenten an 64 kB Grenzen im Speicher, liegt am Ende einer Komponente immer ein ungenutzter Speicherbereich, der allerdings immer zusammen mit der Komponente in den Cache geladen wird. Da Komponenten häufig relativ klein sind, eignet sich dieser freie Bereich um Speicheranfragen der Komponente dorthin abzulegen. Die Speicherverwaltung füllt für jede Komponente diesen Bereich mit einem Micro-Heap auf. Für alle weiteren Speicheranfragen werden am Ende des kompilierten Betriebssystems zwei Speicherpools angelegt.

Abbildung 4.2.: Micro-Heaps und Speicherpools

Alle als  $\mu$  dargestellten Speicherbereiche, stehen für einen Micro-Heap.

Speicheranfragen für nicht-gecacheten Speicher werden immer in den Pool für nicht-gecachete Inhalte gelegt. Dieser wird durch die MMU davor geschützt in den Cache geladen zu werden. Dadurch wird verhindert, dass, während ein Cache-Way entsperrt ist, parallele Zugriffe auf einem anderen Kern in diesen Cache-Way abgelegt werden.

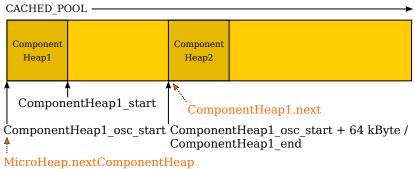

Anfragen für immer-gecacheten Speicher werden zuerst in den Micro-Heap der Komponente gelegt. Falls dieser nicht mehr ausreichend Platz bietet, wird im Pool für gecachete Inhalte ein Component-Heap für die reservierende Komponente angelegt. Dieser hat eine exakte Größe von 64 kB, um in einen Cache-Way geladen werden zu können. Falls auch dieser voll ist, wird ein weiterer Component-Heap angelegt. Die Component-Heaps werden untereinander verkettet, um von einer Komponente jederzeit auf ihre Component-Heaps zugreifen zu können. Dies wird in Abbildung 4.3 veranschaulicht.

Prinzipiell könnten der Pool für gecachete Inhalte und der Pool für nicht-gecachete

Inhalte auch vereinigt werden, da sich der MMU Schutz vor dem Cachen auf einer Granularität von 64 kB einrichten lässt. Davon wird hier allerdings Abstand genommen, da in dem Fall häufig Wartungsoperationen, wie Cache- und TLB-Invalidations anfallen würden. Diese können im Mehrkernbetrieb zu weiteren Problemen führen, die gesondert abgefangen bzw. behandelt werden müssten.

Abbildung 4.3.: Verkettung der Micro-Heaps und Component-Heaps

Jeder Komponente werden ihre eigenen Component-Heaps zugeordnet. In einem Component-Heap liegen daher auch nie Speicherbereiche von verschiedenen Komponenten. Damit wird die physikalische Bindung von reserviertem Speicher an die Komponente sichergestellt. Wenn der Eventhandler reservierten Speicher für eine Komponente lädt, so werden die Component-Heaps genauso wie Komponenten selber in einen freien Cache-Way geladen.

## 4.4. Freispeicherverwaltung

Die Freispeicherverwaltung funktioniert sowohl in den Micro-Heaps, als auch in den Component-Heaps, als auch in dem Pool für nicht-gecachete Inhalte analog. Die Verwaltungsinformationen werden in den reservierten Speicher selbst geschrieben. Dadurch ist es nicht notwendig, die Verwaltungsinformationen zentral zu speichern und diesen zentralen Speicher in den Cache zu laden. Zudem reicht bei dieser Art der Verwaltung die Adresse des reservierten Speichers aus, um alle Verwaltungsinformationen abzurufen.

#### 4.5. Schnittstelle

Die Speicherverwaltung selbst ist keine Anwendungskomponente. Dadurch muss nicht jedes Mal, wenn Speicher reserviert wird eine zusätzliche Komponente in den Cache geladen werden. Des weiteren ist der kompilierte Quellcode der Speicherverwaltung verhältnismäßig klein und würde in einer eigenen Komponente Speicherplatz verschwenden. Aus diesen Gründen wird der Code der Speicherverwaltung den Betriebssystemfunktionen zugeordnet und beim Linken in eben diesen 64 kB Block gelegt.

Anwendungen können vier Funktionen der Speicherverwaltung aufrufen.

#### allocate

```

enum MemoryType {FULLY_CACHED, NOT_CACHED, DYNAMIC_CACHED}

uintptr t allocate(OSC *osc, dword t size, MemoryType type)

```

Mit dieser Funktionen können Anwendungskomponenten Speicherbereiche reservieren. Mithilfe des type Parameter kann bestimmt werden, welcher Speicherklasse der reservierte Speicher zugeordnet werden soll. Der osc Parameter ist eine Referenz auf die reservierende Komponente, damit der Speicher physikalisch und logisch dieser Komponente zugeordnet werden kann. Zudem kann über den osc Parameter ein Zugriff auf den Micro-Heap und die verketteten Component-Heaps erfolgen.

#### free

```

void free(uintptr t memory)

```

Diese Funktion gibt einen reservierten Speicherbereich frei. Dabei werden in dem entsprechenden Speicherblock Regionen gesucht, die vor oder hinter der freizugebenden liegen und eventuell verschmolzen, damit die entstehende Lücke auch für größere Speicheranfragen genutzt werden kann. Wird durch die Freigabe ein Component-Heap geleert, so wird dieser aus der Verkettung entfernt und der Platz im Pool für gecachete Inhalte wieder freigegeben.

## Speicherabhängigkeiten in Triggern

```

void addTriggerDependency(OSC *osc,

EventHandling::Trigger *trigger, uintptr_t memory)

void removeTriggerDependency(OSC *osc,

EventHandling::Trigger *trigger, uintptr_t memory)

```

Diese beiden Funktionen können genutzt werden um Speicherabhängigkeiten für beliebige Trigger einzutragen und wieder zu entfernen.

Mithilfe der allocate und free Funktion werden auch der new und delete Operator von C++ implementiert. Dies ermöglicht es den Anwendungskomponenten, dann Objekte zur Laufzeit anzulegen und zu verwalten. Die Speicherabhängigkeiten kann die Komponente ebenfalls für erzeugte Objekte angeben.

## 5. Implementierung

Die Quellcodes für die Speicherverwaltung sind größtenteils separat in einigen Klassen angelegt. Da die Speicherverwaltung eine Interaktion mit CyPhOS erfordert, befinden sich einige Teile des Quellcodes auch in den Quellcodedateien von CyPhOS. Die bestehenden Linkerskripte wurden so erweitert, dass der kompilierte Code der Speicherverwaltung in die Betriebssystemkomponente integriert wird.

## 5.1. Anlegen der Speicherpools

Die beiden Speicherpools für gecacheten (CACHED\_POOL) und nicht-gecacheten Speicher (NOT\_CACHED\_POOL) müssen hinter dem Ende des kompilierten Betriebssystems angelegt werden. Die Platzierung des Codes in den Speicher erfolgt in drei Linkerskripten, die alle unter arch/armv7/cortexa9 liegen. Das Skript ldscript-end.ld platziert die letzten Inhalte des Betriebssystems am Ende des Speichers. Am Ende dieses Skripts wird noch ein Symbol abgelegt, dessen Adresse im Quellcode bestimmt werden kann. Ab der Adresse dieses Symbols wird der Hauptspeicher von CyPhOS nicht mehr verwendet und die Speicherverwaltung kann die beiden Speicherpools dort anlegen. Das Berechnen der Startadressen der Pools erfolgt aus dem Symbol und der definierten Größenangabe der Pools im Konstruktor der Klasse MemoryAllocator <sup>1</sup>.

In den Pool für gecacheten Speicher werden immer Component-Heaps der Größe 64 kB abgelegt. Zur Verwaltung dieses Pools wird eine Bitmaske angelegt, die für jeden 64 kB Abschnitt des Pool für gecachete Inhalte angibt, ob dieser durch einen Component-Heap belegt ist, oder ob er noch frei ist.

Hinter den beiden Speicherpools wird eine Seitentabelle angelegt, die für die Implementierung des dynamisch gecacheten Speichers (5.5) benötigt wird.

## 5.2. Micro-Heaps und Component-Heaps

Die Verwaltung der Micro-Heaps und Component-Heaps wird durch die Klassen Micro-Heap $^2$  und Component-Heap $^3$  bereitgestellt. Die Instanzen dieser Klassen

<sup>&</sup>lt;sup>1</sup>dynamicmemory/MemoryAllocator.{h,cc}

<sup>&</sup>lt;sup>2</sup>dynamicmemory/MicroHeap.{h,cc}

<sup>&</sup>lt;sup>3</sup>dynamicmemory/ComponentHeap.{h,cc}

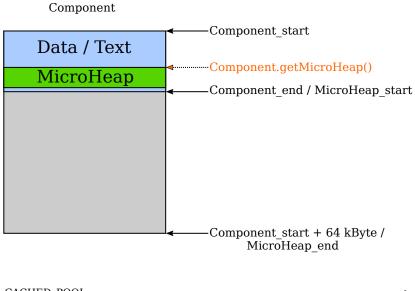

speichern maßgeblich die Startadresse und Endadresse eines freien Speicherbereichs ab. Die Klasse OSC, welche das Grundgerüst für eine Komponente liefert, hat einen Micro-Heap als Attribut. In den Makros zur Erstellung einer Komponente unter component/OSC.h wird dieses Attribut mit den spezifischen Speicheradressen für die Komponente initialisiert. Durch das Linkerskript wird am Ende des kompilierten Codes einer jeden Komponente ein Symbol platziert. Die Adresse dieses Symbols entspricht der Startadresse des Micro-Heaps. Die Endadresse des Micro-Heaps kann aus der Startadresse der Komponente und der Cache-Way Größe berechnet werden. Die Speicherverwaltung kann über die Methode Micro-Heap\*OSC::getMicroHeap() auf die Instanz des Micro-Heaps zugreifen und die Startadresse auslesen, ab der reservierter Speicher platziert werden kann.

Die Klasse ComponentHeap funktioniert ähnlich wie die Klasse MicroHeap. Instanzen dieser Klasse werden von der Speicherverwaltung im Pool für gecachete Inhalte angelegt. Dazu kommt der placement-new Operator zum Einsatz, der ein Objekt an einer vorgegeben Speicheradresse zur Laufzeit erstellt (5.7). Neben der Startadresse des freien Speichers, stellt ComponentHeap noch eine Methode zur Verfügung, die die Startadresse des gesamten Component-Heap, also mit der gespeicherten Instanz der Klasse, angibt. Diese Informationen werden beim Laden eines Component-Heap in den Cache benötigt.

Eine Instanz eines Micro-Heap speichert die Referenz nextComponentHeap ab, mit der die Speicherverwaltung auf die an eine Komponente geketteten Component-Heaps zugreifen kann. Jede Instanz eines Component-Heaps speichert die Referenz next, mit der auf weitere Component-Heaps zugegriffen werden kann.

Eine Übersicht der Funktionen, Adressen und Referenzen ist in Abbildung 5.1 dargestellt.

Abbildung 5.1.: Adressübersicht der Heaps

Das Beispiel zeigt eine Komponente, die zwei Component-Heaps hat. Referenzen sind in orange dargestellt, Adressen in schwarz.

## 5.3. Freispeicherverwaltung

## 5.3.1. Belegung von Speicher

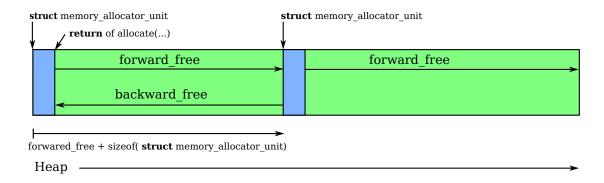

Die Freispeicherverwaltung funktioniert für alle verschiedenen Speichersektionen gleichermaßen. Dazu gehören alle Micro-Heaps, alle Component-Heaps und der gesamte Pool für nicht gecachete Inhalte. Die Verwaltungsinformationen werden vor den reservierten Speicher geschrieben. Dadurch wird kein extra Speicher für die Verwaltung benötigt, die Verwaltungsinformationen werden automatisch mit gecachet und die Verwaltung bleibt dynamisch. Für die Verwaltungsinformationen steht das struct memory\_allocator\_unit <sup>4</sup> bereit. Jede Instanz dieser Datenstruktur enthält folgende Informationen:

- 1. Eine Variable, die angibt, ob der Speicherbereich frei oder benutzt ist

- 2. Eine Referenz auf den Heap, in dem sich dieser Speicherbereich befindet

- 3. Eine Größenangabe, wie groß der freie Speicherbereich ist

- 4. Eine Größenangabe des davor liegenden Speicherbereichs

- 5. Eine Spinlock-Instanz, über die eine Synchronisierung der Speicherzugriffe erfolgt

Jeder Micro-Heap, jeder neu erstellte Component-Heap und der Pool für nichtgecachete Inhalte werden mit einem großen Speicherblock initialisiert. Dieser wird auf nicht benutzt gesetzt. Die Größe des Bereichs errechnet sich aus den Startund Endangaben des Heaps. Sobald Speicher reserviert werden soll, iteriert die Speicherverwaltung über die Speichersektionen. Mithilfe der Größenangabe in der Verwaltungseinheit kann direkt zu der nächsten Verwaltungseinheit gesprungen werden, die den nächsten Block verwaltet. Sobald ein Block gefunden wird, der ausreichend groß ist und der nicht verwendet wird, wird dieser Block als verwendet markiert. Anschließend wird überprüft, ob die verbleibende Größe des freien Speichers ausreichend Platz für eine weitere Verwaltungseinheit und die kleinste reservierbare Einheit Speicher bietet. Ist dies der Fall, so wird am Ende des Blocks ein weiterer Block erstellt, in den Speicheranfragen abgelegt werden können. Je nach angeforderter Speicherklasse, werden verschiedenen Heaps betrachtet:

• Immer im Cache: Zuerst wird nach einem freien Platz im Micro-Heap der Komponente gesucht. Ist dort kein freier Platz, werden alle verketteten Component-Heaps durchsucht. Ist dort auch kein freier Platz, wird ein neuer Component-Heap erstellt und durchsucht. Kann kein neuer Component-Heap erstellt werden, wird die Allokation abgebrochen.

<sup>&</sup>lt;sup>4</sup>dynamicmemory/MemoryPool.h

- Dynamisch gecachet: Der Micro-Heap wird ignoriert, da diese Speicherbereiche nicht durch die MMU überwacht werden. Das Vorgehen erfolgt ansonsten analog zur ersten Speicherklasse.

- Nie gecachet: Der gesamte Pool für nicht-gecachete Inhalte wird wie ein Heap verwaltet. Es wird ein freier Block gesucht. Kann keiner gefunden werden, so wird die Allokation abgebrochen.

Die Verwaltung der Speicherblocks in einem beliebigen Heap wird durch die Funktion searchInHeap <sup>5</sup> implementiert.

## 5.3.2. Freigabe von Speicher

Wird ein benutzter Speicherbereich freigegeben, so überprüft die Speicherverwaltung zuerst, in welchen Heap sich der Speicherblock befindet. Da die Verwaltungsinformationen immer vor den reservierten Speicher geschrieben werden, errechnet sich die Speicherverwaltung die Adresse der zugehörigen Verwaltungseinheit und setzt diese auf nicht benutzt. Mithilfe der Größenangabe des vorherigen Blocks, kann die Speicherverwaltung auch auf die Verwaltungseinheit des vorherigen Blocks zugreifen. Nach dem Freigeben wird sowohl nach vorne, als auch nach hinten iteriert, und eine Folge von nicht belegten Speicherblocks zu einem größeren Block zusammengefasst. Dadurch können später auch größere Speicheranfragen in diesem Block abgelegt werden und die Fragmentierung wird verringert. Diese Funktionalität übernimmt die Funktion freeMAU <sup>6</sup>.

Sobald der Speicherblock freigegeben wurde, findet noch eine Überprüfung statt, ob sich der Speicherbereich in einem Component-Heap befunden hat und ob dieser Component-Heap durch das Freigeben leer geworden ist. Ist dies der Fall, so wird der Platz des Component-Heaps im Pool für gecachete Inhalte wieder freigegeben und der Component-Heap wird aus der Verkettung der anderen Component-Heaps entfernt.

<sup>&</sup>lt;sup>5</sup>dynamicmemory/MemoryAllocatorSystem.cc

<sup>&</sup>lt;sup>6</sup>dynamicmemory/MemoryAllocatorSystem.cc

Abbildung 5.2.: Verwaltungseinheiten in einem Heap

Blau dargestellt sind die Instanzen der Verwaltungseinheit. Grün dargestellt ist der für die Anwendungen verfügbare Speicher.

## 5.4. Cachen von Inhalten

Das aktive Cachen von Speicherbereichen erfolgt immer dann, wenn ein Trigger zur Ausführung kommen soll, für den Speicherabhängigkeiten eingetragen sind, oder wenn ein Zugriff auf einen durch die MMU überwachten Bereich erfolgt. In beiden Fällen wird immer ein gesamter Component-Heap in den Cache geladen. Speicherabhängigkeiten die für Speicherbereiche in einem Micro-Heap eingetragen sind können ignoriert werden, da der Micro-Heap bereits zusammen mit der zugehörigen Komponente geladen wurde.

Das Laden eines Component-Heap erfolgt analog zu dem Laden einer Komponente. Zuerst wird ein freier Cache-Way gesucht. Kann keiner gefunden werden, so wird gemäß der im Betriebssystem vorgegebenen Verdrängungsstrategie eine andere Komponente oder ein anderer Component-Heap verdrängt. Dieser Cache-Way wird entsperrt, sodass der Hardware Cache-Controller Zugriffe in diesen Cache-Way ablegen kann. Anschließend werden für alle Speicherworte des Component-Heaps Preload-Instruktionen aufgerufen, sodass der Hardware-Cache-Controller den Component-Heap gezwungenermaßen in den freien Cache-Way legt. Sind alle Preload-Instruktionen abgeschlossen, so wird der Cache-Way wieder gesperrt. Diese Funktionalität implementiert die Funktion preloadOSCHeap <sup>7</sup>.

$<sup>^7</sup>$ arch/armv7/driver/ARMv7CacheControl\_critical.cc

## 5.5. Dynamisch gecachete Speicher (Access-Flag)

Wird "dynamisch gecachet" bei der allocate Funktion angefragt, so ist das Programmverhalten nahezu identisch, als wenn immer gecacheter Speicher angefragt wird. Der einzige Unterschied besteht darin, dass der Micro-Heap der Komponente nicht in Betracht gezogen wird, um die Speicheranfrage abzulegen. Dies ist dadurch bedingt, dass nur der Pool für gecachete Inhalte durch die MMU überwacht wird und nur dort Speicherzugriffe festgestellt werden können. Wird eine Speicherabhängigkeit für einen dynamisch gecacheten Speicherbereich angegeben, so wird der entsprechende Component-Heap ebenso vor der Ausführung des Trigger vorgeladen, wie bei immer gecachetem Speicher. Ebenso werden auch Component-Heaps auf Zugriffe überwacht, in denen immer gecacheter Speicher liegt und für diese keine Speicherabhängigkeiten eingetragen sind. Das dynamische Laden in den Cache kann allerdings nicht für alle Speicherbereiche aus der Klasse "immer im Cache" sichergestellt werden, da immer gecachete Speicherbereiche auch in den Micro-Heaps liegen können.

Zur Überwachung des Pool für gecachete Inhalte kommt das Access-Flag zum Einsatz [1]. Das Access-Flag ist ein Bit im Seitentabelleneintrag einer Speichersektion. Wird ein Eintrag mit diesem Bit auf 0 gesetzt in den Translation-Look-Aside-Buffer (TLB) geladen, so wird ein Access-Flag-fault ausgelöst, welches durch eine Unterbrechungsbehandlung behandelt werden kann. Das Access-Flag kann nicht standardmäßig genutzt werden. Die Voraussetzungen sind eine aktivierte MMU mit einer Seitentabelle und das explizite Aktivieren des Access-Flag durch das Systemkontrollregister. CyPhOS verwendet standardmäßig eine Seitentabelle mit einer Seitengröße von 1 MB. Dies ist zur Überwachung einzelner Component-Heaps mit einer Größe von 64 kB ungeeignet. Daher muss eine Second-level Seitentabelle eingerichtet werden, die 64 kB große Seiten verwaltet und für jede Seite ein Access-Flag bereitstellt.

## 5.5.1. Aktivieren des Access-Flag

CyPhOS stellt bereits Funktionen zur Verfügung, die die Seitentabelle aufsetzen und die MMU aktivieren. Zuerst muss die bestehende Seitentabelle so verändert werden, dass alle Access-Flags auf 1 stehen, damit nicht direkt nach der Aktivierung des Access-Flag Access-Flag-faults ausgelöst werden. Dies wird in der Funktion resetAllAccessFlags <sup>8</sup> erledigt. In der bereits vorhandenen Funktion enableMMU wird das Systemkontrollregister geschrieben, um das Access-Flag zu aktivieren. CyPhOS ruft diese Funktion bereits auf allen Kernen auf.

<sup>&</sup>lt;sup>8</sup>arch/armv7/driver/ARMMMU.cc

Zuletzt muss noch die Second-level Seitentabelle eingerichtet werden, die eine Granularität von 64 kB ermöglicht. Die Adressen des Pool für gecachete Inhalte werden so ausgelegt, dass sie an 1 MB Grenzen ausgerichtet sind. In der first-level Seitentabelle muss für jede 1 MB Seite ein Referenzeintrag auf die second-level Seitentabelle eingerichtet werden. Die Ausrichtung des Pool für gecachete Inhalte an 1 MB Grenzen ermöglicht es also eine second-level Seitentabelle nur für den Pool für gecachete Inhalte einzurichten. Sowohl das Aufsetzen der second-level Tabelle als auch das Setzen der Referenzeinträge in der first-level Seitentabelle wird in der Funktion init <sup>9</sup> implementiert. Die Access-Flags der second-level Seitentabelle werden initial alle auf 0 gesetzt, da keine unkontrollierten Zugriffe in den Pool für gecachete Inhalte erfolgen.

Die Steuerung dieser Abläufe hintereinander erfolgt in der von CyPhOS zur Verfügung gestellten Funktion init\_primary\_cpu\_c <sup>10</sup>.

## 5.5.2. Nutzung des Access-Flag

Im initialen Zustand nach dem Start von CyPhOS sind alle Access-Flags des Pool für gecachete Inhalte auf 0 gesetzt. Demnach würden bei jedem Zugriff in diesen Pool Access-Flag-faults ausgelöst. Wird ein Component-Heap nun in den Cache geladen, so wird das Access-Flag auf 1 gesetzt. Wird dieser Pool gemäß der Verdrängungsstrategie wieder aus dem Cache verdrängt, so wird das Access-Flag wieder auf 0 gesetzt. Beides erfolgt in den Funktionen preloadOSCHeap <sup>11</sup> und getLRUWay <sup>12</sup>. Während der Erstellung eines Component-Heap wird das Access-Flag ebenfalls auf 1 gesetzt, da Zugriffe in den Heap nötig sind, aber keine Erforderlichkeit besteht den Heap in der nächsten Zeit in den Cache zu laden. Dadurch erfolgen zwar Hauptspeicherzugriffe, diese haben an dieser Stelle allerdings keine negative Auswirkung, da das Zeitverhalten beim Allozieren keine Zeitgarantie zur Verfügung stellt. Auch Interferenzen mit dem Preloading können nicht auftreten, da ein Spinlock sicherstellt, dass während einer Speicherallokation kein Preload stattfindet.

## 5.5.3. Behandlung des Access-Flag-fault

Wird ein Access-Flag-fault ausgelöst, so wird eine Data-abort-exception ausgelöst, für die CyPhOS eine rudimentäre Behandlungsroutine anbietet. Diese Routine wird so erweitert, dass sie die Funktion handleDataAbortException <sup>13</sup> aufruft.

$<sup>^9 {\</sup>tt dynamic memory/MemoryAllocator System.cc}$

$<sup>^{10} {\</sup>tt arch/armv7/cortexa9/boot/initOS.cc}$

$<sup>^{11} {\</sup>tt arch/armv7/driver/ARMv7CacheControl\_critical.cc}$

$<sup>^{12}</sup>$ arch/armv7/driver/ARMv7CacheControl\_critical.cc

$<sup>^{13}</sup>$ dynamicmemory/MemoryAllocatorSystem.cc

Das data-fault-address-register (DFAR) beinhaltet die Adresse, die zu dem Dataabort geführt hat. Dem data-fault-status-register (DFSR) kann entnommen werden, ob die data-abort-exception durch ein Access-Flag-fault ausgelöst wurde. Die

Behandlungsfunktion liest diese beiden Register aus und überprüft ob es sich um

ein Access-Flag-fault handelt und ob die Fehler-verursachende Adresse aus dem

Pool für gecachete Inhalte stammt. Ist dies der Fall, wird der Component-Heap,

aus dem diese Adresse stammt, mit der Funktion preloadOSCHeap in einen freien

Cache-Way geladen. Dadurch wird das Access-Flag dieses Heaps auf 1 gesetzt.

Nach dem zurückkehren in die Behandlungsroutine von CyPhOS wird der Programmzähler auf seinen gesicherten Wert gesetzt und das Programm an der Stelle

fortgesetzt, an der die Unterbrechung aufgetreten ist.

## 5.6. Nicht gecacheter Speicher

Alle Aufrufe der allocate Funktion, die nicht gecacheten Speicher anfordern werden in den Pool für nicht-gecachete Inhalte abgelegt. Dieser wird genauso verwaltet wie ein Heap. In der init Funktion, die während des Startvorgangs aufgerufen wird, wird ein Schutz für den Pool für nicht-gecachete Inhalte eingerichtet. In der first-level Seitentabelle wird in jedem Tabelleneintrag, der auf den Pool für nicht-gecachete Inhalte verweist, ein Bit gesetzt welches das Cachen dieser Sektion verbietet. So können im Mehrkern-Betrieb Anwendungen weiterhin auf nicht gecacheten Speicher zugreifen, ohne das Preloading auf einem anderen Kern zu stören. Für nicht gecacheten Speicher erfolgt keine Zugriffskontrolle und kein aktives Vorladen.

## 5.7. new-Operator

CyPhOS ist zum größten Teil in C++ geschrieben. Daher ist es für Anwendungskomponenten möglich Klassen zu definieren und Objekte dieser Klassen zu erstellen. Ohne die dynamische Speicherverwaltung müssen zur Übersetzungszeit alle Objekte feststehen. Durch den new-Operator ist es möglich Objekte auch dynamisch zur Laufzeit zu erstellen. Dabei ist zwischen dem new-Operator und dem new-Ausdruck zu unterscheiden [5]. Wird das new Schlüsselwort in einer Programmzeile verwendet, so interpretiert der Compiler dies als den new-Ausdruck. Der new-Ausdruck benötigt den new-Operator, um den für das Objekt benötigten Speicherplatz zu reservieren. Durch den new-Ausdruck wird in dem reservierten Speicher anschließend das Objekt angelegt. Spezifisch implementiert werden muss nur der new-Operator, der den Speicher reserviert. Dies erfolgt in der Datei common/new.{h, cc}. Die new-Operatoren rufen lediglich die allocate Funktion der Speicherverwaltung auf, geben die entsprechenden Argumente weiter und

geben einen Pointer auf den reservierten Speicher zurück. Zusätzlich wird noch ein placement-new Operator definiert, dem als Parameter bereits eine Adresse angegeben werden kann, an die das Objekt gelegt wird. Des Weiteren gibt es einen new-Operator, dem als Parameter zusätzlich ein Pointer auf eine Adressvariable übergeben werden kann. In diese Variable schreibt der Operator die reservierte Speicheradresse. Dies ist wichtig, da der new-Ausdruck, der in einem Anwendungsprogramm steht, nicht zwangsweise einen Pointer auf den reservierten Speicherbereich liefert. C++ platziert die Objekte teilweise mit einem Offset in dem reservierten Speicher und gibt einen Pointer auf das Objekt zurück. Zum Angeben von Speicherabhängigkeiten oder zum Freigeben von Speicher wird aber der Beginn der reservierten Sektion benötigt.

Der delete-Operator ist analog mit der free Funktion implementiert.

Zur direkten und einfachen Nutzung der Speicherverwaltung und des new-Operator, wird eine doppelt verkettete Liste implementiert, die den new-Operator zum Erstellen von neuen Elementen verwendet. Die Implementierung dieser Liste erfolgt in der Datei common/LinkedList. {h, cc}.

## 5.8. Speicherabhängigkeiten

Das unter Kapitel 4 dargestellte Konzept der Speicherklassen wird im Bezug auf die Speicherabhängigkeiten in der Implementierung erweitert. Wird eine Speicherabhängigkeit angegeben, so wird der entsprechende Speicher vor der Ausführung des Trigger auf jeden Fall in den Cache geladen. Es ist demnach möglich auch Speicher, der aus der Klasse "dynamisch gecachet" reserviert wurde, nicht erst bei einem Zugriff in den Cache zu laden. Wird für einen Speicherbereich aus der Klasse "immer im Cache" keine Abhängigkeit angegeben, so wird dieser Speicher auch nicht vor der Ausführung des Trigger in den Cache geladen.

Speicherabhängigkeiten können für immer gecachete und dynamisch gecachete Speicherbereiche angegeben werden. Die addTriggerDependency <sup>14</sup> Funktion betrachtet hierbei nur Speicheradressen, die aus dem Pool für gecachete Inhalte stammen. Soll eine Speicherabhängigkeit definiert werden, die aus einem Micro-Heap einer anderen Komponente stammt, so muss diese Komponente sowieso als Abhängigkeit des Trigger der ersten Komponente angegeben werden und wird somit bei der Ausführung dieses Trigger in den Cache geladen. CyPhOS verlangt bei der Initialisierung eines Trigger bereits ein Array von Komponenten, die in den Cache geladen werden müssen wenn der Trigger zur Ausführung kommt. Abhängigkeiten für Speicher im Micro-Heap können auf diese Art definiert werden. Jeder Trigger hat eine Liste als Attribut, in der die Speicherabhängigkeiten gespeichert werden, die über die addTriggerDependency Funktion angegeben werden.

<sup>&</sup>lt;sup>14</sup>dynamicmemory/MemoryAllocator.cc

Der dynamisch allozierte Speicher für diese Listen wird immer aus der Kategorie "immer im Cache" in der Betriebssystemkomponente reserviert. In der Funktion preloadOSC <sup>15</sup> wird über die Liste des Trigger iteriert, der zur Ausführung kommen soll. Alle Elemente führen zu einem Aufruf der preloadOSCHeap Funktion, sodass alle abhängig markierten Speicher garantiert im Cache liegen, wenn der Trigger ausgeführt wird. Am Ende des Aufrufs der addTriggerDependency Funktion, wird die preloadOSC Funktion zusätzlich manuell aufgerufen, denn es besteht die Möglichkeit, dass eine Speicherabhängigkeit definiert wurde, die auf den Trigger zutrifft, in dem diese Definition stattfindet. Bevor die nächste Instruktion dieses Trigger stattfinden darf, muss diese Abhängigkeit also erfüllt werden. Neben dem Preloading in den Cache, sollen die Speicherabhängigkeiten noch eine Synchronisierungsfunktion erfüllen. Das heißt, es dürfen nicht zwei Trigger gleichzeitig ausgeführt werden, die eine gemeinsame Speicherabhängigkeit haben. Dies wird durch einen Spinlock in jedem reservierten Speicherabschnitt realisiert. Der Scheduler ruft die Funktion tryTaskLock <sup>16</sup> auf. Nur wenn diese Funktion true zurückgibt, kommt der entsprechende Trigger zur Ausführung. Diese Funktion wird so erweitert, dass sie versucht alle Spinlocks der Speicherabhängigkeiten für diesen Trigger zu belegen. Ist dies nicht erfolgreich, werden die belegten Spinlocks wieder gelöst und der Vorgang abgebrochen. Da diese Prozedur für jeden Trigger ausgeführt wird, ist die Synchronisierung sichergestellt. Um die Funktionalität zu gewährleisten werden alle Locks nach der Ausführung des Trigger wieder freigegeben. Dies geschieht in der Funktion handlerFinished <sup>17</sup>.

Für Speicherbereiche für die keine Speicherabhängigkeiten angegeben werden, wird systemseitig keine Synchronisierung bereitgestellt.

#### 5.8.1. Kohärenz im Translation-Look-Aside-Buffer

Jeder CPU-Kern hat einen eigenen TLB. Seitentabelleneinträge mit einem Access-Flag von 0 werden niemals in den TLB geladen. Wird im Betriebssystem nun ein Component-Heap verdrängt und sein Access-Flag wieder auf 0 gesetzt, so ist es möglich, dass in einigen TLBs noch der fehlerhafte Eintrag steht und auch nicht aktualisiert wird. Um dem Vorzubeugen, wird der TLB nach dem Verdrängen auf allen Kernen invalidiert. Dazu kommt das Maintenance-Operation-Broadcasting zum Einsatz, welches die Cortex-A9 Spezifikation implementiert [3]. Daraus ergibt sich ein weiteres Problem. Finden auf einem Kern aktuell Speicherzugriffe statt, und wird dieser Speicher nun durch ein Programm auf einem anderen Kern verdrängt, so wird das Access-Flag für den Speicher, auf den aktuell zugegriffen wird, zurückgesetzt und der TLB geleert. Geschieht dies während einer Zugriffsoperation, so wird nicht ein erneutes Access-Flag-fault ausgelöst, sondern die Ausführung

$<sup>^{15} {\</sup>tt arch/armv7/driver/ARMv7CacheControl\_critical}$

<sup>16</sup> eventhandling/EventHandler.cc

<sup>&</sup>lt;sup>17</sup>eventhandling/EventHandler.cc

bricht mit einer prefetch-abort-exception ab. Dies kann nur verhindert werden, wenn sichergestellt ist, dass keine Inhalte verdrängt werden, auf die aktuell zugegriffen wird. Die Verwaltung der Cache-Ways verdrängt keine Speicherinhalte, die gelockt sind. Speicherinhalte werden aber nur gelockt, wenn eine Komponente zur Ausführung kommt, die diese Speicherinhalte als Abhängigkeit eingetragen hat. Der Anwendungsentwickler muss demnach sicherstellen, dass, wenn Komponenten zur Ausführung kommen, die Speicher verwenden, für die sie keine Abhängigkeit eingetragen haben, keine Verdrängungen stattfinden können. Da Verdrängungen hauptsächlich beim Kontextwechsel stattfinden, muss die Ausführungsreihenfolge eventuell synchronisiert werden.

Für die relevanten Systemfunktionen, die auch Speicher verdrängen würden (z. B. erfordert das Locken von Speicherabhängigkeiten vor der Ausführung einer Komponente Zugriffe in den Speicher selber, da dort die Locks platziert sind) wird das Access Flag auf dem aktuellen Kern deaktiviert und anschließend wieder aktiviert. Damit können die Systemfunktionen auf Speicher zugreifen, ohne dabei anderen Speicher verdrängen zu müssen.

# 6. Anwendungsbeispiel: CAN-Bus

Das folgende Kapitel beschreibt beispielhaft die Nutzung der Speicherverwaltung für eine Anwendungskomponente. In Abbildung 4.1 ist eine mögliche Anwendung der Speicherverwaltung bereits symbolisch dargestellt. Diese Anwendung ist exemplarisch in CyPhOS implementiert, um ein Beispiel für die Verwendung der Speicherverwaltung bereit zu stellen.

## 6.1. Der CAN-Treiber

Der CAN-Treiber ist bereits in CyPhOS in der Klasse MCP2515SPI <sup>1</sup> implementiert. Dieser bietet verschiedene Trigger an, um Nachrichten auf den CAN-Bus zu senden und um Diese zu empfangen. Zur Nutzung mit der Speicherverwaltung wird der Treiber um den Trigger trigger\_sendMessageFromMemory erweitert. Diese erwartet als Argument die Speicheradresse einer vordefinierten Datenstruktur, in der alle Informationen über die zu sendende Nachricht abgelegt sind. Eine Instanz von dieser Datenstruktur kann von einer Komponente angelegt werden und anschließend die Adresse dem Trigger übergeben werden.

## 6.2. Anwendungskomponente: Gangwahlschalter

Die Klasse GearSelector <sup>2</sup> implementiert die Steuerung eines Gangwahlschalter über den CAN-Bus. Dazu verwendet diese den CAN-Treiber und den Trigger trigger\_sendMessageFromMemory. Im Start Trigger der Klasse werden Speicherbereiche aus der Klasse "dynamisch-gecachet" für die verschiedene Nachrichten reserviert. Es werden Abhängigkeiten sowohl für den Trigger trigger\_sendMessage-FromMemory, als auch für den Trigger receiveGear angegeben. Dies sorgt dafür, dass der Speicher für die zu sendenden CAN-Nachrichten im Cache liegt, wenn die Klasse GearSelector diese mit Nachrichten beschreibt und wenn der CAN-Treiber aus dem Speicher liest, um die Nachricht zu versenden. Da der reservierte Speicher aus der Klasse "dynamisch gecachet" stammt, können die

<sup>&</sup>lt;sup>1</sup>arch/armv7/imx6/driver/MCP2515SPI.{h,cc}

<sup>&</sup>lt;sup>2</sup>autolabcomponents/GearSelector.{h,cc}

Inhalte nur aus Component-Heaps stammen. Die Anwendung braucht demnach keine Komponentenabhängigkeit für den Trigger zu definieren, die die gesamte GearSelector Komponente in den Cache laden würde, wenn der Trigger zur Ausführung kommt. Würde der Speicher aus der Klasse "immer im Cache" stammen, so müsste die Komponente GearSelector in das Abhängigkeitsarray des Trigger trigger\_sendMessageFromMemory eingetragen werden. Dadurch würde bei jeder Ausführung des Trigger trigger\_sendMessageFromMemory die Komponente GearSelector mit in den Cache geladen und somit auch die Speicherinhalte, die in ihrem Micro-Heap stehen.

Das Versenden einer Nachricht erfordert in dieser Implementierung mehrere Codezeilen, die sich für verschiedene Nachrichten kaum unterscheiden. Zum vereinfachten Versenden der Nachrichten steht daher das Makro SEND\_CAN\_MESSAGE—WITH\_MEMORY <sup>3</sup> zur Verfügung.

<sup>&</sup>lt;sup>3</sup>arch/armv7/imx6/driver/MCP2515SPI.h

# 7. Evaluation

Um die Leistungsfähigkeit der Speicherverwaltung zu evaluieren, werden folgende Punkte genauer untersucht.

- 1. Unterschiede in den Zugriffszeiten der verschiedenen Speicherklassen.

- 2. Veränderungen der Zugriffszeiten bei parallel stattfindenden Speicherzugriffen.

- 3. Vergleich der Zugriffszeiten mit reinem Hardware-Cache-Management

- 4. Verhalten der Vorladezeiten der Komponenten bei parallel stattfindenden Speicherzugriffen

## 7.1. Konstruierte Testumgebung

Zum Evaluieren der Speicherverwaltung werden Komponenten implementiert, die Speicher reservieren und auf Diesen zugreifen und dabei die Zugriffszeiten messen. Gesteuert werden diese Tests aus der Klasse MemoryEvaluator <sup>1</sup>. Ein einfaches Zugriffsmuster wird in der Klasse MemoryEvalMultipool <sup>2</sup> implementiert. Dabei werden 16 Pools einer bestimmten Größe reserviert und gemäß einer vorgegebenen, nicht sequentiellen Reihenfolge Inhalte von einem in den anderen Pool kopiert. Dadurch werden sequentielle Speicherzugriffe größtenteils vermieden und es können realistische Messwerte erzielt werden. Die Ergebnisse der Messung werden in einem reservierten Speicher aus der Klasse "nie im Cache" abgespeichert und nach dem Test über die serielle Schnittstelle übertragen. Durch das Ablegen der Messdaten im Pool für nicht-gecachete Inhalte wird die Cache-Verwaltung nicht zusätzlich belastet und die Messdaten nicht verfälscht.

Zur Untersuchung der Zugriffszeiten unter parallel stattfindenden Speicherzugriffen wird die Klasse MemoryEvalDisturber <sup>3</sup> verwendet. Diese liest aus einem reservierten Speicherpool Daten aus und schreibt diese nach einer Rechnung wieder in den Pool. Der Pool kann aus verschiedenen Speicherklassen stammen.

Kommt es bei den Tests zu Verdrängungen, so sind die durch die Implementierung

<sup>&</sup>lt;sup>1</sup>testcomponents/MemoryEvaluator.{h,cc}

<sup>&</sup>lt;sup>2</sup>testcomponents/MemoryEvalMultipool.{h,cc}

<sup>3</sup>testcomponents/MemoryEvalDisturber.{h,cc}

der Speicherverwaltung gegebenen Vorgaben zu beachten. Die Speicherinhalte, auf denen die Zeit gemessen wird, sind als Triggerabhängigkeit für den messenden Trigger eingetragen. Demnach hat das Vorladen des Speichers keinen Einfluss auf die Messung, da die Inhalte vor der Ausführung des Triggers und somit vor Beginn der Messung vorgeladen werden, und der Speicher kann während der Messung zudem nicht verdrängt werden. Wird ein Test durchgeführt, bei dem das System über seine Grenzen hinaus belastet wird, so werden für die störenden Speicherbereiche keine Abhängigkeiten eingetragen, da sie sonst nicht im Lauf eines Trigger aus dem Cache verdrängt werden können, um Platz für weitere Speicherbereiche zu schaffen. Dies führt aber auch dazu, dass die Störung erst gestartet werden kann, wenn die zu testende Komponente bereits läuft, da ansonsten durch das Preloading der Komponente ein Speicherbereich verdrängt werden könnte, auf den die Störung gerade zugreift.

Alle hier dargestellten Messungen sind auf einem Odroid U3 Board mit einem Samsung Exynos 4412 Prozessor durchgeführt.

## 7.2. Auswertung der Messungen

Da es sich bei CyPhOS um ein Echtzeitbetriebssystem handelt ist die Vorhersagbarkeit von Zugriffszeiten von besonderem Interesse. Daher wird in den folgenden Messungen insbesondere der Mittelwert und die Varianz untersucht. Für eine Prognose der Zugriffszeiten würde der Mittelwert als Erwartungswert herangezogen. Die durchschnittliche prozentuale Abweichung von diesem Erwartungswert wird im folgenden als Maß für die Vorhersagbarkeit aus dem Erwartungswert verglichen. Die prozentuale Abweichung ist durch den Variationskoeffizienten (Standardabweichung) gegeben.

Für die gemessenen Werte werden einige statistische Kennzahlen (Mittelwert  $(\mu)$ , Varianz  $(\sigma^2)$ , Standardabweichung  $(\sigma)$  und der Variationskoeffizient  $(\sigma/\mu)$ ) tabellarisch im Anhang A dargestellt. Zur Veranschaulichung der Daten kommen zusätzlich Boxplots und Histogramme zum Einsatz.

Bei den Messungen für gecacheten Speicher werden meistens zwei oder mehrere Häufungspunkte zu erkennen sein, um die die Zugriffszeiten schwanken. Diese lassen sich zum Teil durch Level-1 und Level-2 Hits erklären. Bei der Berechnung des Variationskoeffizienten ergibt sich dadurch eine höhere Schwankung als eigentlich berücksichtigt werden muss. Im Sinne der Vorhersagbarkeit von Zugriffszeiten sind Ausreißer nach unten prinzipiell unkritisch. Daher wird bei den entsprechenden Messungen der Variationskoeffizient auch immer für den größten Häufungspunkt der Messungen angegeben um eine Vergleichbarkeit mit den anderen Messungen zu ermöglichen.

7.3 Evaluation

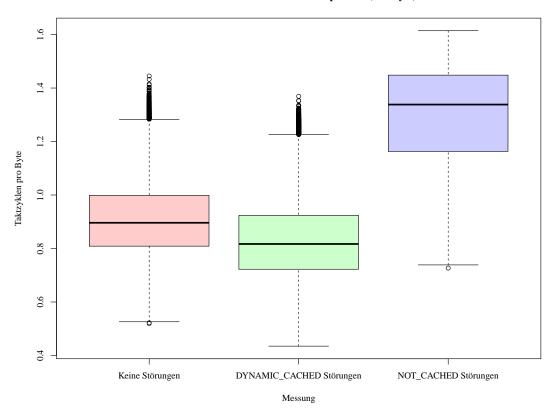

# 7.3. Zugriffszeiten in den verschiedenen Speicherklassen

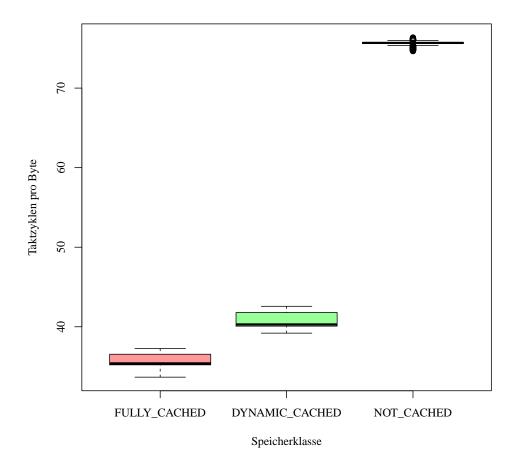

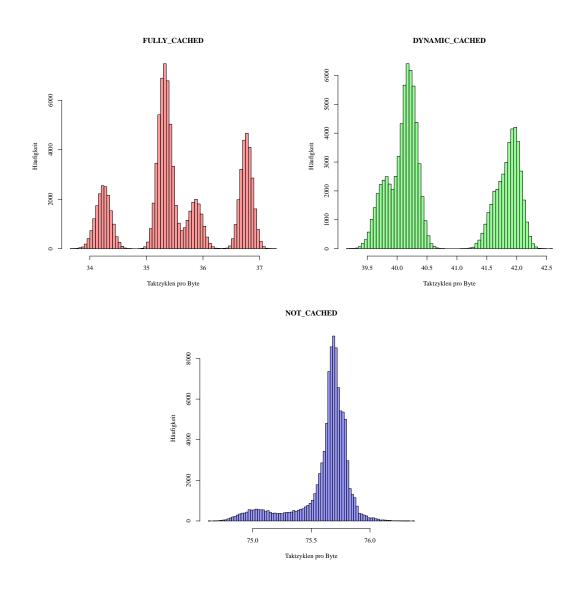

An dieser Stelle werden die Zugriffe ohne Störung untersucht. Dies entspricht einer Anwendung, die alleine auf dem System ausgeführt wird. Der Zugriff wird dabei auf 16 Pools der Größe 16 kB (16384 Byte) getestet. Die Messung wird für jede Speicherklasse 100000 mal durchgeführt. Die Ergebnisse werden in Taktzyklen für das Kopieren eines Bytes von einem in den anderen Pool umgerechnet.

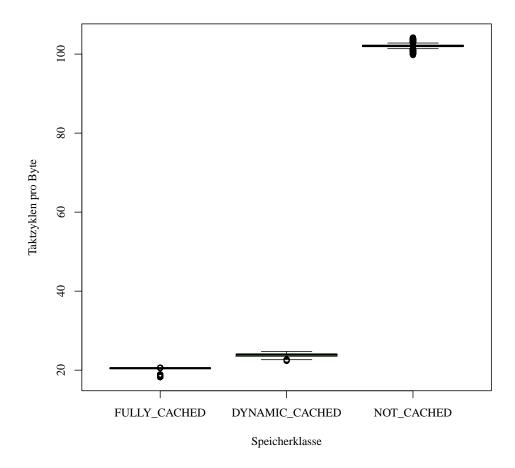

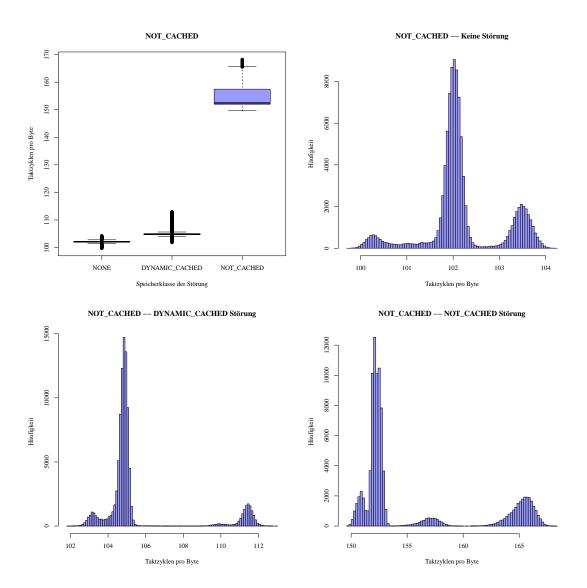

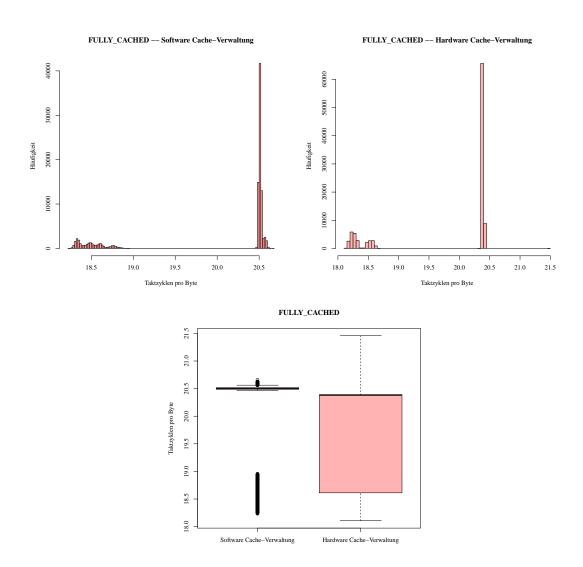

Abbildung 7.1.: Boxplots aller Zugriffszeiten

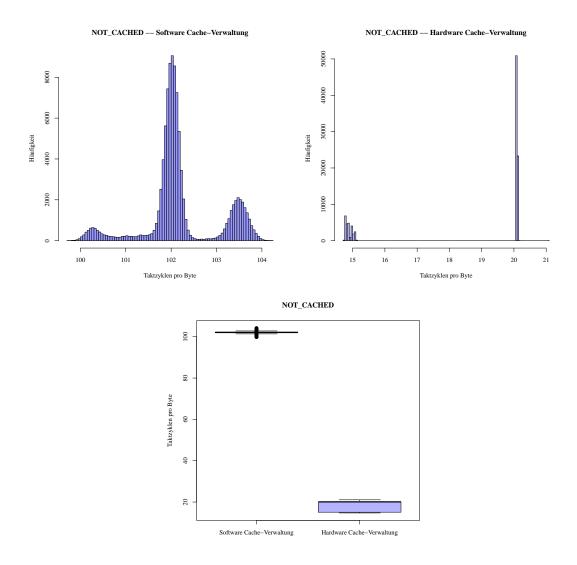

Deutlich zu erkennen ist der Unterschied zwischen gecachetem und nicht-gecachetem Speicher. Speicher, der in dem Pool für nicht-gecachete Inhalte abgelegt wird, wird weder in den L1-Cache, noch in den L2-Cache geladen.

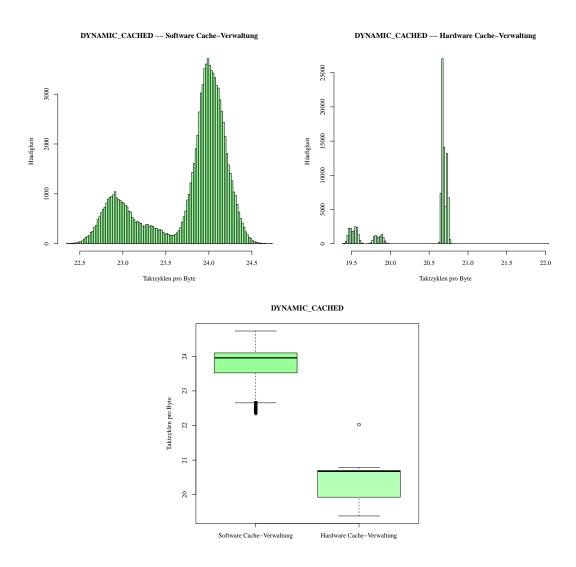

Der Unterschied der Zugriffszeiten zwischen immer-gecachetem und dynamischgecachetem Speicher entsteht durch die unterschiedliche Platzierung der Inhalte. Bei der Allokation von immer-gecachetem Speicher werden einige Inhalte in den Micro-Heap der Komponente gelegt, andere Inhalte liegen in Component-Heaps im Pool für gecachete Inhalte . Bei der Allokation von dynamisch-gecacheten Inhalten liegen hingegen alle Inhalte in Component-Heaps im Pool für gecachete Inhalte. Die Speicherinhalte liegen aufgrund dessen anders strukturiert im Speicher. Verschiedene Effekte können beim Laden in den Cache dafür sorgen, dass eine unterschiedliche Ausrichtung der Inhalte zu unterschiedlichen Zugriffszeiten führt.

7.3 Evaluation

Abbildung 7.2.: Histogramme aller Zugriffszeiten

Aus den Messungen lässt sich erkennen, dass nicht-gecacheter Speicher sowohl im Mittelwert, als auch in der Schwankung deutlich schlechter abschneidet als gecacheter Speicher. Dynamisch gecacheter Speicher weist etwas höhere Zugriffszeiten und eine etwas höhere Schwankung auf, als immer-gecacheter Speicher. Die durchschnittlich Abweichung übersteigt 0.5% allerdings in beiden Klassen nicht.

# 7.4. Zugriffszeiten unter parallel stattfindenden Zugriffen

## 7.4.1. Keine Verdrängungen im Cache

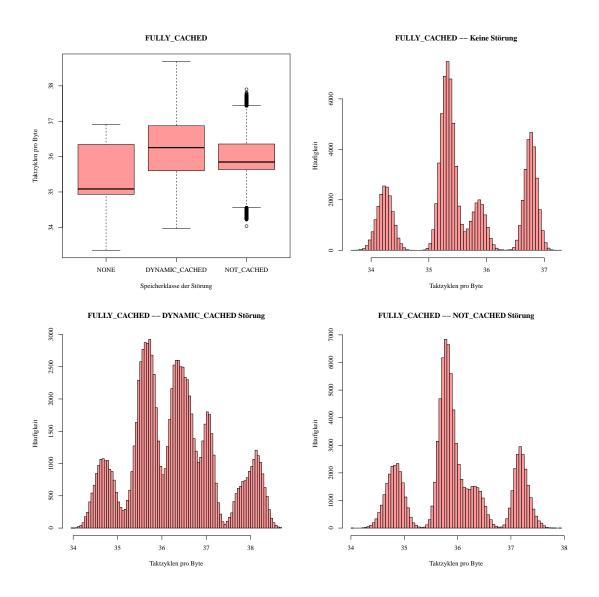

In den folgenden Messreihen wird untersucht, wie groß der Einfluss von parallel stattfindenden Speicherzugriffen auf die Zugriffszeiten ist. Die resultierenden Werte sind vergleichbar mit dem Mehrkern Betrieb von mehreren Anwendungen. Die Messungen werden insbesondere mit Kapitel 7.3 verglichen. Somit kann festgestellt werden, wie robust sich die Zugriffszeiten unter Störung verhalten. Die Zugriffszeiten werden exakt wie in Kapitel 7.3 gemessen. Während jeder Zeitmessung kommt ein weiterer Trigger zur Ausführung, der in vier 32 kB (32768 Byte) großen Pools Daten kopiert. Sowohl die Messung, als auch die Unterbrechung kommen zeitgleich auf verschiedenen Kernen zur Ausführung. Es wird jeweils eine Messung durchgeführt, in der der parallel Zugriffe auf gecacheten und auf nichtgecacheten Speicher erfolgen. In diesem Test können alle Inhalte, auf die Zugriffe erfolgen, dauerhaft im Cache liegen.

Aus den gemessenen Daten lässt sich erkennen, dass auf gecachete Speicherinhalte ein paralleler Zugriff auf weitere gecachete Speicherinhalte einen größeren Einfluss hat, als ein paralleler Zugriff auf nicht-gecachete Speicherinhalte. Dies lässt sich durch die höhere Last an dem Cache-Controller erklären.

Die Einflüsse auf den gecacheten Speicher durch einen parallelen Zugriff halten sich absolut in geringem Maße. Der Erwartungswert der Zugriffszeiten steigt höchstens um wenige Taktzyklen pro Byte und auch die gemessene Schwankung bleibt bei allen Störungen deutlich unter 1% des Erwartungswert. Dies zeigt, dass sich Zugriffszeiten auf gecachete Speicherinhalte auch im parallelen Betrieb stabil verhalten. Auch bei Störungen schneidet der immer-gecachete Speicher etwas besser ab, als der dynamisch-gecachete Speicher. Der Erwartungswert und auch die erwartete Schwankung steigen stärker an, als bei immer-gecachetem Speicher. Nicht-gecachete Speicherinhalte hingegen reagieren empfindlich auf weitere Zugriffe auf nicht-gecachete Inhalte. Dieses Verhalten ist durch die höhere Belastung des Speicherbus zu erklären. Sowohl der Erwartungswert, als auch die erwartete Schwankung steigen deutlich an.

7.4 Evaluation

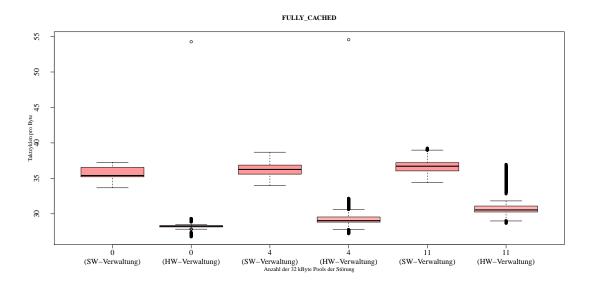

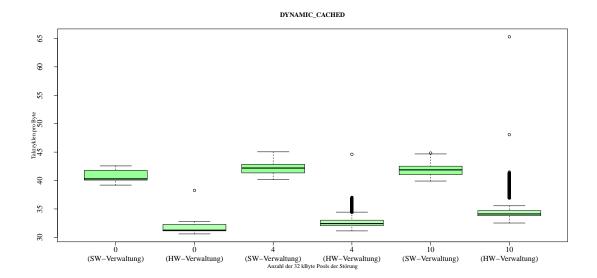

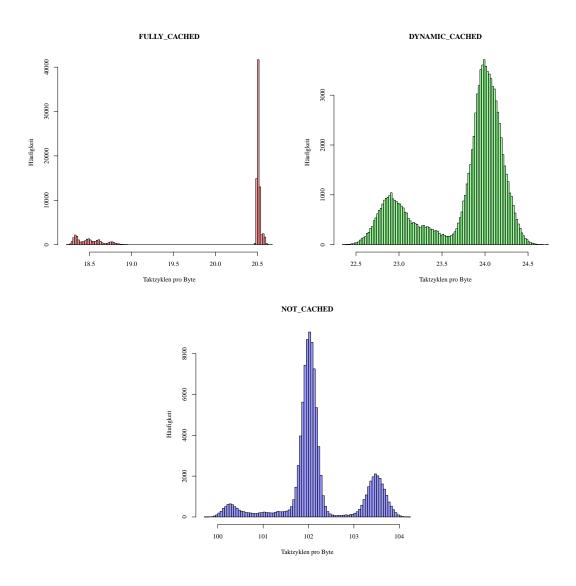

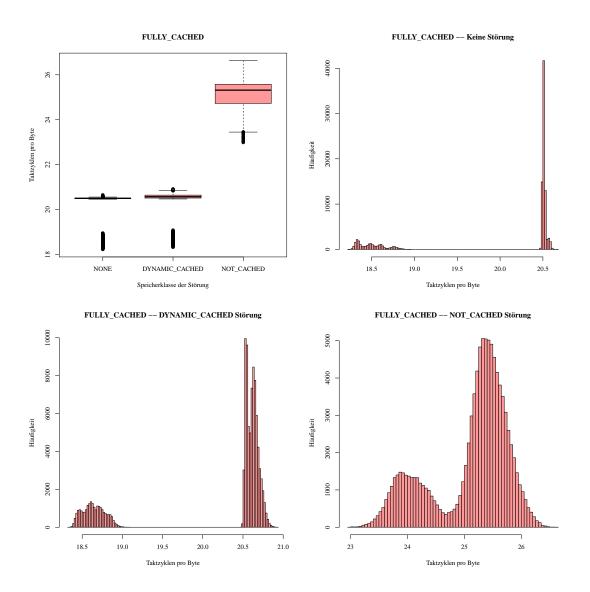

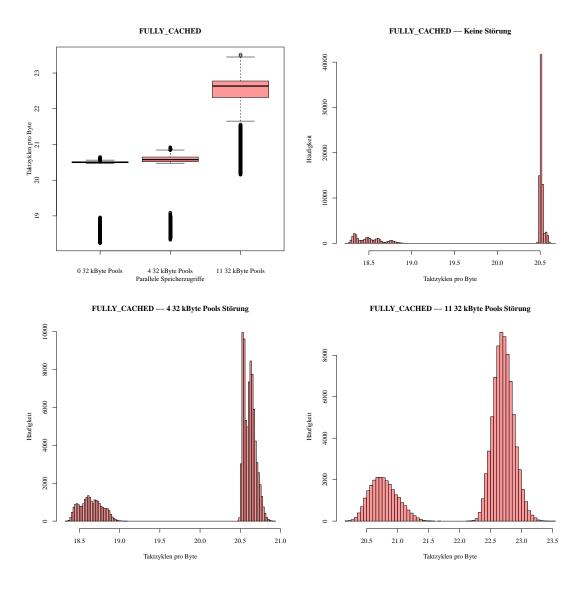

Abbildung 7.3.: FULLY\_CACHED Speicher unter Störungen

Auffällig ist, dass die Verteilung der Zugriffszeiten unter den Störungen ähnlich ist, wie ohne Störungen. Sowohl in den Histogrammen, als auch in dem Boxplot ist zu erkennen, dass die parallel stattfindenden Zugriffe einen eher geringen Einfluss auf die Zugriffszeiten vornehmen.

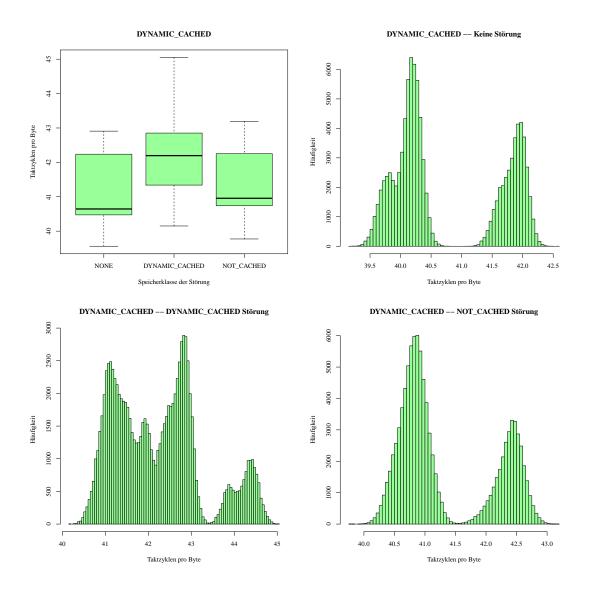

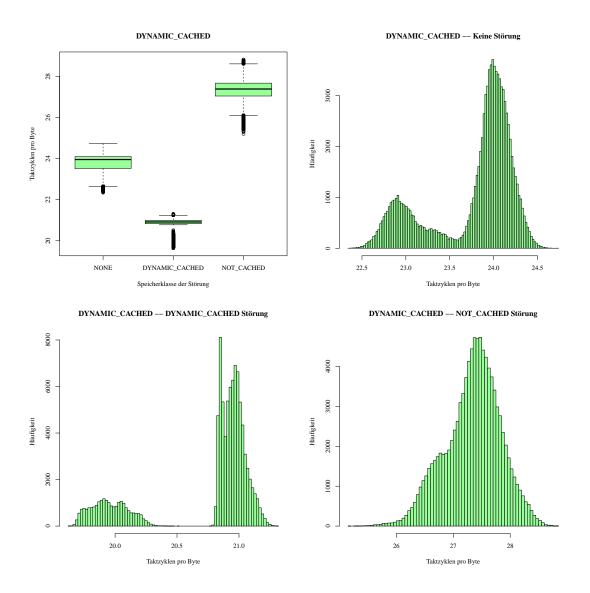

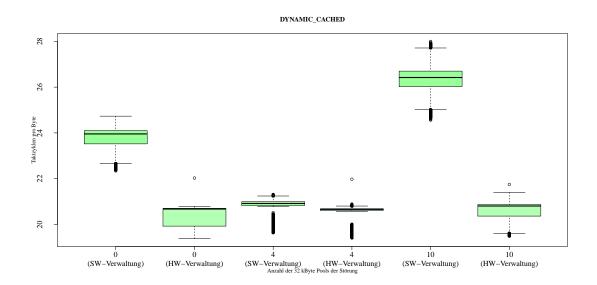

Abbildung 7.4.: DYNAMIC\_CACHED Speicher unter Störungen

Der dynamisch-gecachete Speicher verhält sich unter parallel stattfindenden Speicherzugriffen sehr ähnlich, wie immer-gecacheter Speicher (Abbildung 7.3). Die Verteilung der Zugriffszeiten verändert sich allerdings unter parallel stattfindenden Zugriffen auf gecacheten Speicher stärker.

7.4 Evaluation

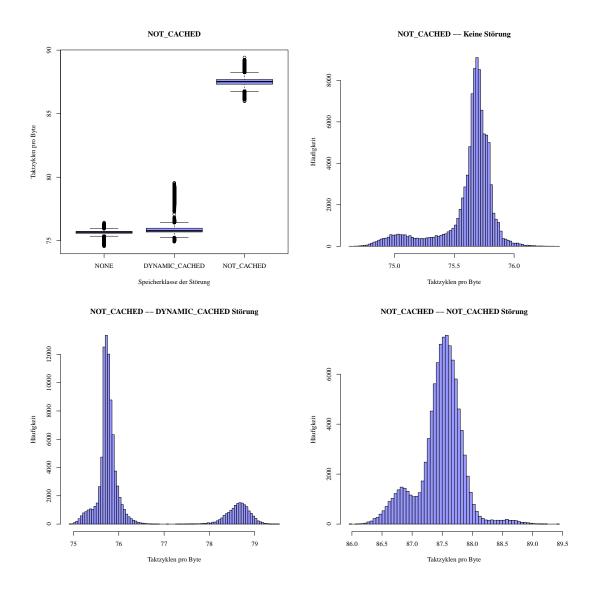

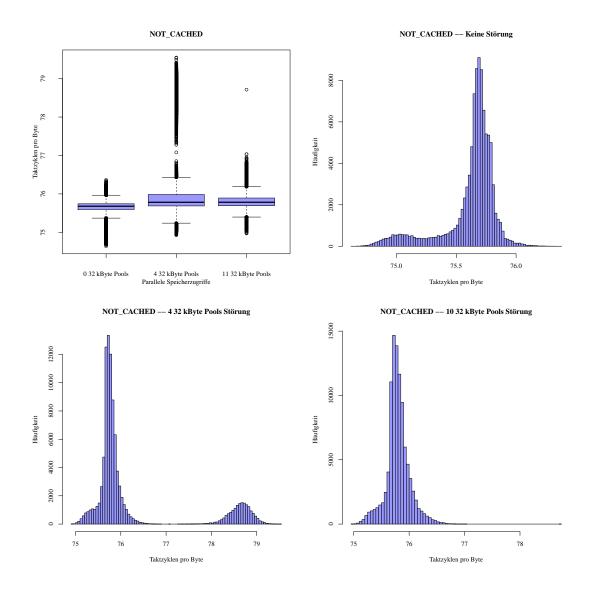

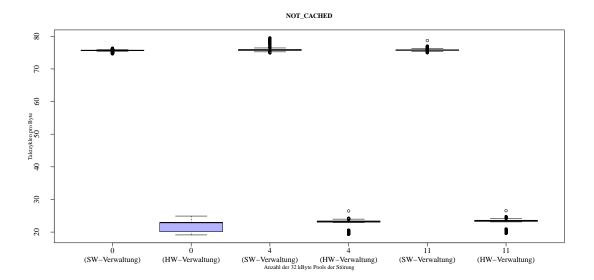

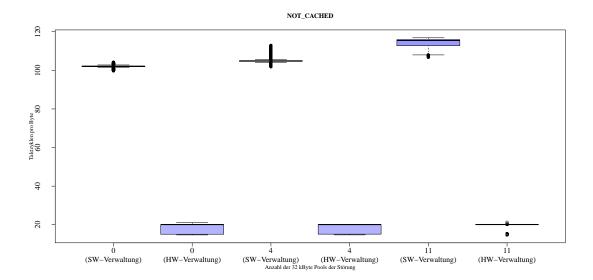

Abbildung 7.5.: NOT\_CACHED Speicher unter Störungen

In dem Boxplot lässt sich besonders gut erkennen, dass nicht-gecacheter Speicher besonders empfindlich auf parallele Zugriffe auf nicht-gecacheten Speicher reagiert. Die Zugriffszeiten werden deutlich größer und schwanken auch stärker. Dies unterstützt die Hypothese, dass ein Echtzeitverhalten im Mehrkern Betrieb erreicht werden kann, wenn parallele Zugriffe auf den Hauptspeicher durch den gemeinsamen Bus vermieden werden können.

## 7.4.2. Verdrängungen im Cache

In den nachfolgenden Messungen werden die selben Zugriffszeiten wie in Kapitel 7.4.1 gemessen. Die parallel stattfindenden Speicherzugriffe werden allerdings verändert, so dass nicht auf vier, sondern auf elf bzw. zehn 32 kB große Pools parallel zugegriffen wird. Dies führt dazu, dass während jeder Messung die Speicherinhalte aus dem Cache verdrängt werden, da die Cache-Ways gemäß der LRU-Strategie verteilt werden. Dieser Test simuliert eine extreme Nutzung des Betriebssystems. Wie bereits in Kapitel 7.1 ausgeführt, sind für die Speicherbereiche des Tests Triggerabhängigkeiten eingetragen, sodass diese nicht verdrängt werden können, während die Zugriffszeit gemessen wird. Es werden nur Cache-Ways verdrängt, in denen Inhalte stehen, die von der störenden Komponente stammen oder nicht mehr benötigt werden.

Aus den Messungen geht hervor, dass das Betriebssystem auch unter übermäßiger Belastung noch geringe Zugriffszeiten gewährleisten kann. Dieses Ergebnis ergibt sich allerdings nur, da die zu testenden Inhalte priorisiert wurden, da sie durch die Speicherabhängigkeiten vor einer Verdrängung geschützt wurden. Die zusätzliche Belastung durch das ständige Verdrängen und Nachladen auf einem CPU-Kern wirkt sich auf die zu testende Komponente nur sehr gering aus. Der Mittelwert der Zugriffszeiten steigt höchstens um wenige Taktzyklen und auch die Schwankung steigt um weniger als 1% des Mittelwerts.

7.4 Evaluation

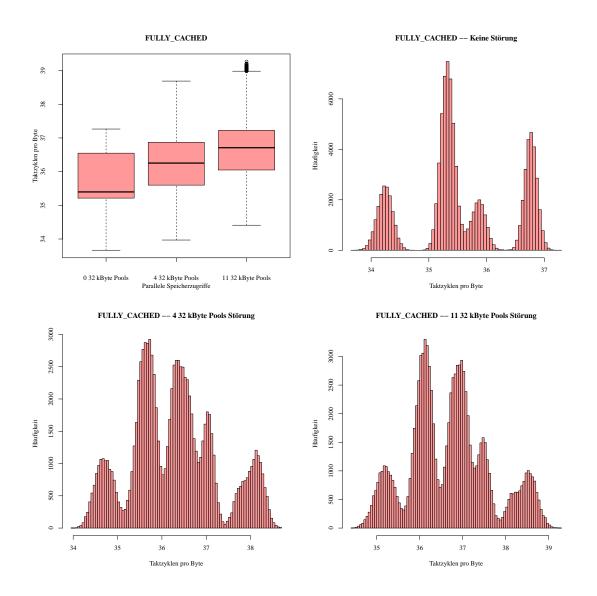

Abbildung 7.6.: FULLY\_CACHED Speicher im parallelen Betrieb

In dem Boxplot lässt sich gut erkennen, dass sich die Zugriffszeiten auch unter steigender paralleler Last stabil verhalten. Das Maximum steigt dabei auch nur um ca. 2 Taktzyklen an. Auch die Histogramme zeigen, dass sich die Verteilung der Zugriffszeiten nicht stark verändert. Diese Beobachtungen sprechen dafür, dass mit dieser Implementierung der Speicherverwaltung die Effekte des parallelen Betriebs größtenteils abgeschirmt werden können, so wie CyPhOS es bereits für die Ausführung von Anwendungen tut.

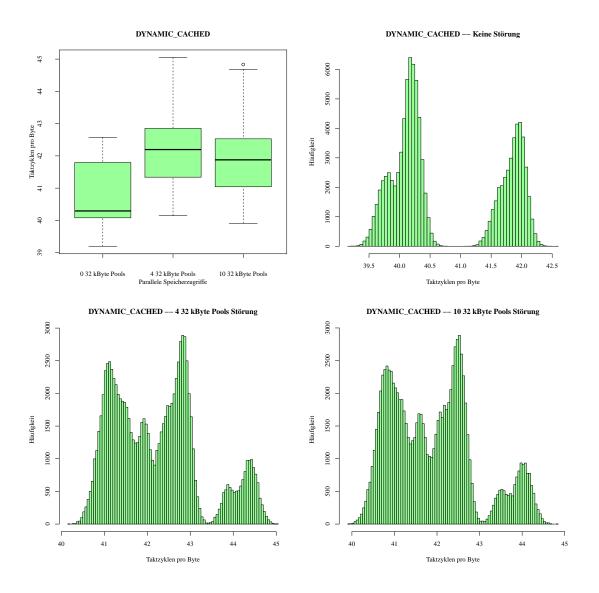

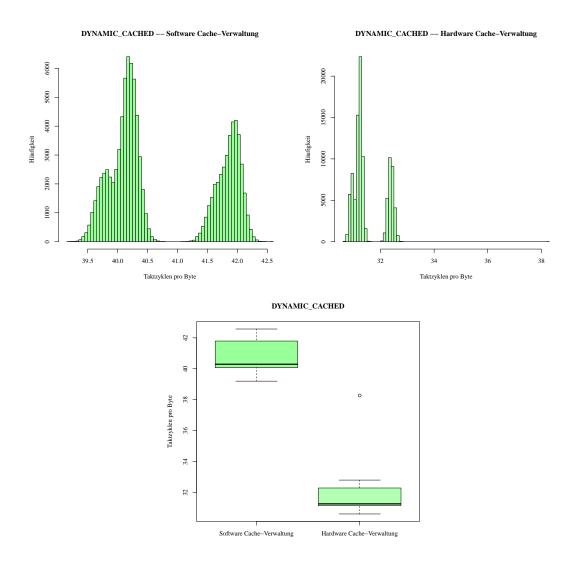

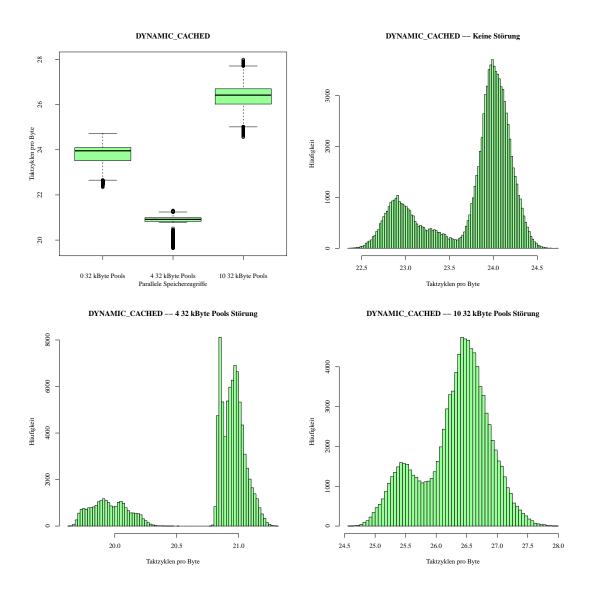

Abbildung 7.7.: DYNAMIC\_CACHED Speicher im parallelen Betrieb

Die Zugriffszeiten auf Speicher aus der Klasse "dynamisch-gecachet" verhalten sich sehr ähnlich den Zugriffszeiten für die Klasse "immer im Cache" (Abbildung 7.6). Die Zugriffszeiten unterscheiden sich auch hier nur um wenige Taktzyklen. Auffällig erscheint in dem Boxplot, dass die Zugriffszeiten unter stattfindender Verdrängung scheinbar geringer werden. Bei genauerer Analyse der Histogramme stellt sich die Verteilung der Zugriffszeiten allerdings nahezu identisch heraus, wie die unter geringer paralleler Last. Das Bild im Boxplot kann durch die etwas andere Verteilung entstehen.

7.4 Evaluation

Abbildung 7.8.: NOT\_CACHED Speicher im parallelen Betrieb

Der Einfluss von parallel stattfindenden Speicherzugriffen auf gecacheten Speicher zeigt sich erwartungsgemäß gering auf die Zugriffszeiten auf nicht-gecacheten Speicher. Finden Verdrängungen statt, so erfolgen durch das Vorladen zwar Zugriffe in den Hauptspeicher, diese sind allerdings sequentiell und verhältnismäßig selten.

# 7.5. Vergleich mit reinem Hardware-Cache-Management

In den nachfolgenden Tests werden einige der Messungen aus Kapitel 7.3 und Kapitel 7.4 wiederholt. Diesmal wird die Software-Cache-Kontrolle von CyPhOS deaktiviert. Somit übernimmt der Hardware-Cache-Controller des Exynos Prozessors die Verwaltung der L2-Cache-Ways. Anhand dieser Ergebnisse wird beurteilt, inwiefern die Software-Cache-Kontrolle besser funktioniert als ein nicht aktiv kontrollierter Cache.

## 7.5.1. Kein paralleler Betrieb (vgl. Kapitel 7.3)

Für die nachfolgenden Messreihen werden die Zugriffszeiten für die verschiedenen Speicherklassen ohne eine parallele Störung gemessen. Die Größe der Speicherpools entspricht exakt den Testbedingungen aus Kapitel 7.3.

In allen Testreihen fällt auf, dass die Hardware-Verwaltung einen deutlich geringeren Mittelwert aufweist. Wird die Software-Verwaltung verwendet, so wird auch eine virtuelle Speicheradressierung verwendet. Dies erhöht die Zugriffszeiten. Die prozentuale Schwankung ist bei dem Test mit dynamische gecachetem Speicher unter Hardware-Verwaltung etwas geringer, übersteigt aber in allen Tests nie 0.7% (für den größten Häufungswert). Der massive Unterschied bei den nicht-gecacheten Speicherinhalten rührt daher, dass bei einer reinen Hardware-Cache-Verwaltung Inhalte nicht explizit vom Caching ausgeschlossen werden. Die Speicherinhalte werden also trotzdem in den Cache gelegt.

7.5 Evaluation

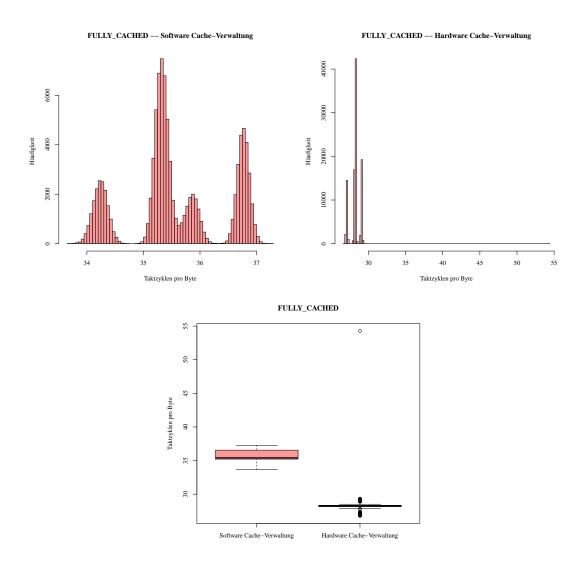

Abbildung 7.9.: FULLY\_CACHED Speicher Hardware / Software verwaltet

Aus dem Histogramm lässt sich erkennen, dass der Maximalwert deutlich weiter vom Mittelwert entfernt liegt, wenn die Hardware-Cache-Verwaltung zum Einsatz kommt ( $\mu \approx 35$  und  $max \approx 37$  bei Software-Verwaltung,  $\mu \approx 28$  und  $max \approx 54$  bei Hardware-Verwaltung). Dies liegt daran, dass bei reiner Hardware-Cache-Verwaltung Inhalte verdrängt werden können, während die Komponente noch läuft. Dies führt bei dem nächsten Zugriff dann zu einem Ausreißer, da der Inhalt erst wieder in den Cache geladen werden muss. Dieses Verhalten wird bei der Software-Cache-Verwaltung aktiv verhindert.

Abbildung 7.10.: DYNAMIC\_CACHED Speicher Hardware / Software verwaltet

Ähnlich wie bei immer-gecachetem Speicher (Abbildung 7.9) ist der Maximalwert bei der Hardware-Cache-Verwaltung im Vergleich zum Mittelwert deutlich größer als bei der Software-Cache-Verwaltung ( $\mu \approx 40$  und  $max \approx 42$  bei Software-Cache-Verwaltung,  $\mu \approx 31$  und  $max \approx 38$  bei Hardware-Cache-Verwaltung). Der hohe Maximalwert kommt auch hier durch Ausreißer zustande, bei denen Inhalte während der Ausführung eines Trigger aus dem Cache verdrängt wurden und dann bei einem Zugriff erst wieder vorgeladen werden müssen. Die Software-Verwaltung schließt ein Verdrängen der Inhalte aus, während der Trigger in Betrieb ist.

7.5 Evaluation

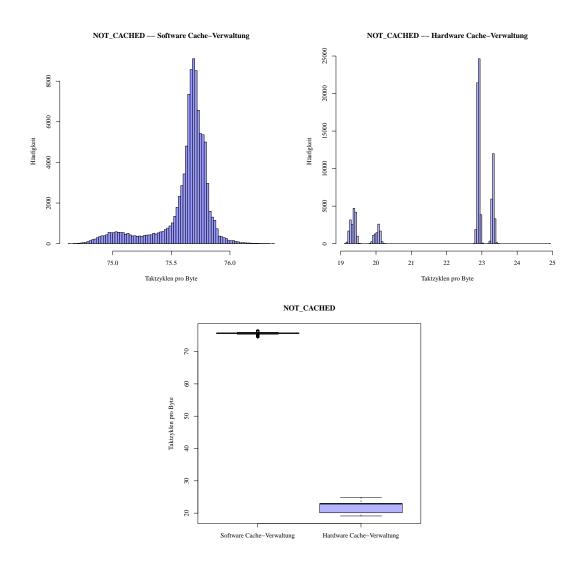

Abbildung 7.11.: NOT\_CACHED Speicher Hardware / Software verwaltet

Der große Unterschied zwischen Software-Verwaltung und Hardware-Verwaltung liegt darin begründet, dass Speicherinhalte bei der Software-Verwaltung explizit vom Laden in den Cache ausgeschlossen werden. Bei der Hardware-Verwaltung hingegen werden diese Speicherinhalte wie alle anderen behandelt.

## 7.5.2. Paralleler Betrieb (vgl. Kapitel 7.4)

In dieser Testreihe wird abermals untersucht, wie sich die Zugriffszeiten im parallelen Betrieb verändern. Dabei wird die Software-Cache-Verwaltung mit der Hardware-Cache-Verwaltung verglichen. Zum Ermitteln der Zugriffszeiten kommt die selber Testumgebung wie in Kapitel 7.4 zum Einsatz. Eine Störung durch Zugriffe in nicht-gecacheten Speicher kann an dieser Stelle nicht verglichen werden, da dieser Test mit der Hardware-Cache-Verwaltung nicht durchgeführt werden kann.

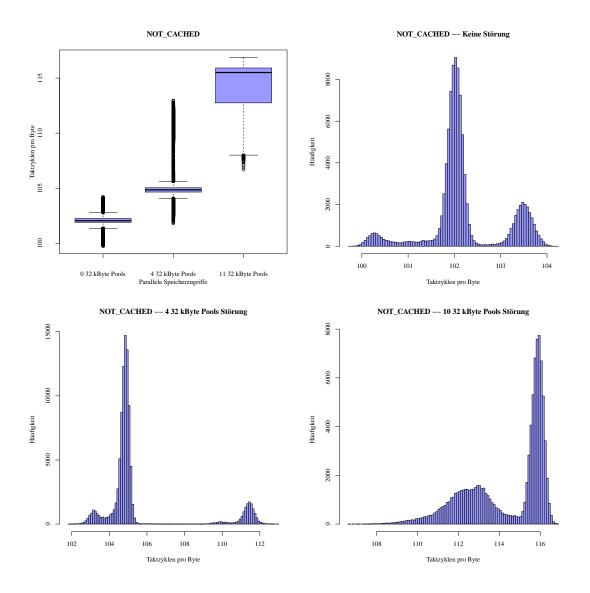

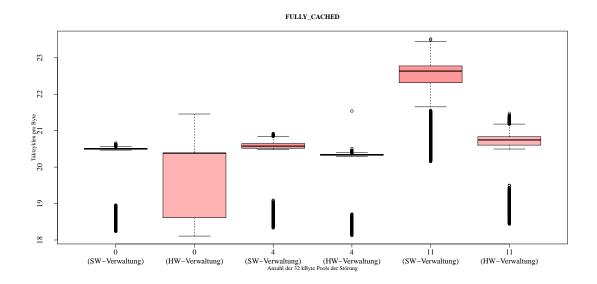

Abbildung 7.12.: FULLY\_CACHED Speicher unter Störungen (Hardware und Software verwaltet)

Auffällig ist, dass bei allen Testreihen mir Hardware-Cache-Verwaltung die Zugriffszeiten im Mittel niedriger liegen als bei Verwendung der Software-Cache-Verwaltung, die Streuung allerdings größer ist. In allen Tests treten bei der Hardware-Cache-Verwaltung mehr Ausreißer auf, die auch weiter vom Mittelwert weg streuen. Im extrem parallelen Betrieb (11 parallel zugegriffene Pools) sind in der Messreihe der Hardware-Cache-Verwaltung extrem viele Ausreißer zu beobachten, in der Messreihe der Software-Cache-Verwaltung sind hingegen nur sehr wenige Ausreißer zu finden. Auch die Differenz der Mittelwerte bzw. Mediane zwischen Hardware- und Software-Verwaltung ist im extrem parallelen Betrieb erheblich geringer. Die Zugriffszeiten bleiben bei der Software-Cache-Verwaltung demnach stabiler, wenn die parallele Auslastung des Systems steigt, als es die Zugriffszeiten bei der Hardware-Cache-Verwaltung tun.

7.5 Evaluation

Abbildung 7.13.: DYNAMIC\_CACHED Speicher unter Störungen (Hardware und Software verwaltet)

Die Messungen unterscheiden sich prinzipiell nicht von den Messungen für immergecacheten Speicher (Abbildung 7.12). Die Hardware-Cache-Verwaltung behandelt ohnehin alle Speicherklassen gleich und auch bei der Software-Cache-Verwaltung gibt es nur geringfügige Unterschiede in der Verwaltung, die die Zugriffszeiten beeinflussen könnten.

Abbildung 7.14.: NOT\_CACHED Speicher unter Störungen (Hardware und Software verwaltet)

In diesen Messungen besteht zwischen Hardware und Software-Verwaltung ein großer Unterschied, da die Hardware-Cache-Verwaltung die Inhalte gleichermaßen in den Cache lädt, wie alle anderen Inhalte auch. Die Auswirkungen im parallelen Betrieb lassen sich somit nicht vergleichen.

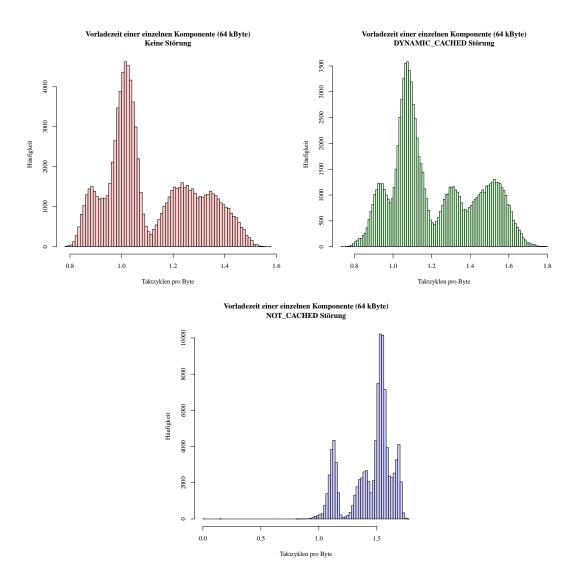

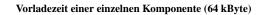

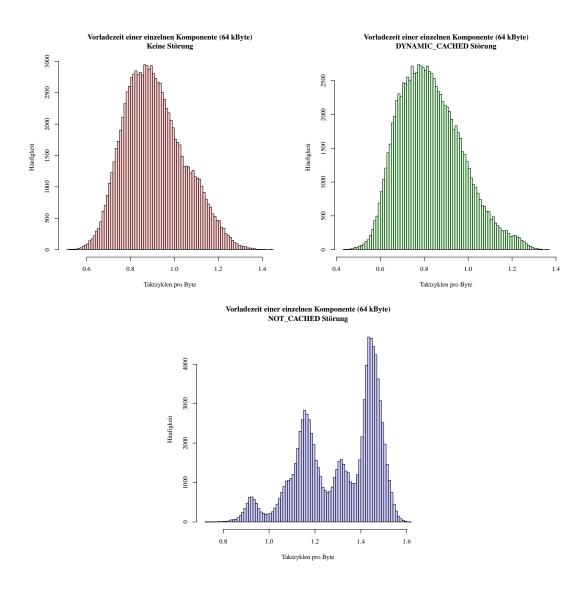

# 7.6. Verhalten der Vorladezeiten der Komponenten

In der letzten Testreihe wird untersucht, welchen Einfluss die Nutzung der Speicherverwaltung auf das Vorladen der Komponenten in den Cache hat. Die Komponente MemoryEvalOSCPreload <sup>4</sup> ist eine speziell angelegte Testkomponente, für die die Vorladezeit gemessen wird, wenn der Trigger do\_the\_work zur Ausführung kommt. Dieser Test wird 100000 mal wiederholt.

Um den Einfluss des parallelen Betriebs zu untersuchen, kommt abermals die Komponente MemoryEvalDisturber <sup>5</sup> zum Einsatz. Während der Messung der Vorladezeit wird auf einem anderen CPU-Kern auf Speicherpools zugegriffen, die aus allen 3 Speicherklassen stammen können. Für den Test wird zur parallelen Störung auf 6 Pools der Größe 32 kB zugegriffen.

Damit auch bei jedem Test die Komponente tatsächlich komplett in den Cache geladen wird und nicht schon Bereits Inhalte der Komponente im Cache liegen, wird

<sup>&</sup>lt;sup>4</sup>testcomponents/MemoryEvalOSCPreload.{h,cc}

<sup>&</sup>lt;sup>5</sup>testcomponents/MemoryEvalDisturber.{h,cc}

7.6 Evaluation

nach jeder Messung der Trigger cleanup der Komponente MemoryEvalOSCClean <sup>6</sup> ausgeführt. Dieser alloziert Speicher über die Speicherverwaltung aus der Klasse dynamisch-gecachet. Diese reservierten Speicher werden bei der Reservierung sofort in den Cache geladen, dadurch wird die zu testende Komponente aus dem Cache verdrängt.

# Keine Störungen DYNAMIC\_CACHED Störungen Messung

#### Vorladezeit einer einzelnen Komponente (64 kByte)

Abbildung 7.15.: Boxplots der Vorladezeiten unter Störungen

Gut zu erkennen ist, dass die Vorladezeiten in allen Tests um ca. 1 Taktzyklus pro Byte schwanken. Die stärkste Auswirkung hat ein paralleler Zugriff auf nicht-gecacheten Speicher, da sich dann dieser Zugriff und das Vorladen den Speicherbus teilen müssen. Auch Zugriffe auf gecacheten Speicher haben eine Auswirkung, denn der Cache-Controller wird dabei einer höheren Last ausgesetzt. Insgesamt halten sich die Auswirkungen von parallelem Betrieb in engen Grenzen.

<sup>&</sup>lt;sup>6</sup>testcomponents/MemoryEvalOSCClean.{h,cc}

Abbildung 7.16.: Histogramme der Vorladezeiten