## Masterarbeit

Laufzeitüberwachung eingebetteter Systeme zur Detektion von Softwarefehlern mit AspectC++

Software-Fault Detection in Embedded Systems by Runtime Monitoring with AspectC++

Simon Dierl 21. August 2018

Betreuer:

Prof. Dr.-Ing. Olaf Spinczyk M. Sc. Ulrich Thomas Gabor

Technische Universität Dortmund Fakultät für Informatik Lehrstuhl 12 Arbeitsgruppe Eingebettete Systemsoftware https://ess.cs.tu-dortmund.de

#### **Abstract**

In the development and maintenance of software, the localization of the root cause of bugs is challenging and time-consuming. Spectrum-based fault localization automates identification of root causes by analyzing a set of test runs. Execution of the runs has to be triggered manually.

To automate the process, this thesis employs automation to gather relevant information from a single continuous execution. The automation is extended to operate without domain knowledge by inferring models from well-behaving software and detect deviant behavior by runtime model checking. To this purpose, driver interaction models are introduced to describe the interactive behavior of drivers and peripheral components.

Empirical examination demonstrated the feasibility of the approach. Driver interaction models were able to detect over  $50\,\%$  of the introduced defects and spectrum-based fault localization was subsequently able to identify the defect's location with near-perfect accuracy. Domain-agnostic approaches appear to be a useful extension to spectrum-based fault localization, while the technique itself is applicable in embedded scenarios. The applications of driver interaction models warrant further study.

# **Contents**

| 1 | Intr | oduction                          | 1  |

|---|------|-----------------------------------|----|

|   | 1.1  | Objectives                        | 3  |

|   | 1.2  | Contributions                     | 3  |

|   | 1.3  | Structure of this Work            | 4  |

| 2 | Spe  | ctrum-Based Fault Localization    | 5  |

|   | 2.1  | Standard Terminology for Defects  | 5  |

|   | 2.2  | Basic Concepts                    | 7  |

|   | 2.3  | Suspiciousness Metrics            | 8  |

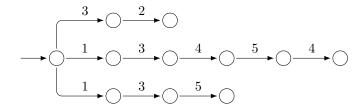

|   | 2.4  | Method Call Sequence Hit Spectra  | 10 |

|   | 2.5  | Parameter Classification          | 11 |

|   | 2.6  | Thread-Aware Analysis             | 12 |

| 3 | SBF  | FL in Long-Running Systems        | 13 |

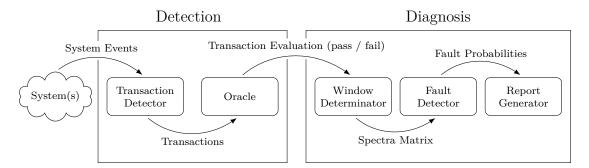

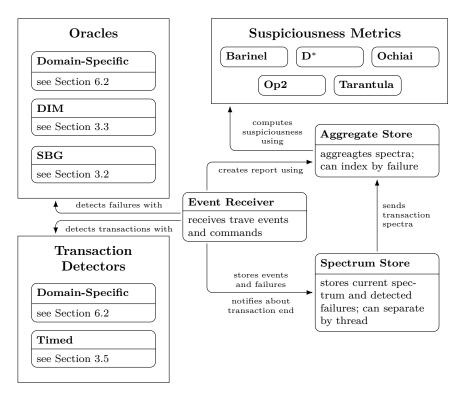

|   | 3.1  | Oracles and Transaction Detectors | 13 |

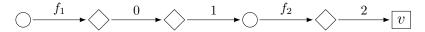

|   | 3.2  | Software Behavior Graphs          | 14 |

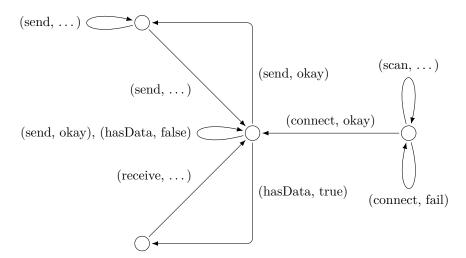

|   | 3.3  | Driver Interaction Models         | 15 |

|   | 3.4  | Learning DIMs                     | 18 |

|   | 3.5  | Timer-Based Transactions          | 21 |

|   | 3.6  | Failure-Specific Analysis         | 21 |

| 4 | AOI  | P-Based Instrumentation           | 23 |

|   | 4.1  | Basic Concepts                    | 23 |

|   | 4.2  | AspectC++                         | 24 |

| 5 | lmp  | lementation                       | 27 |

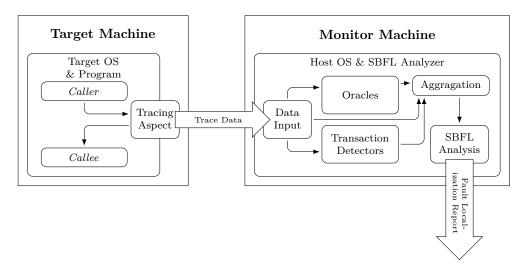

|   | 5.1  | Architecture                      | 27 |

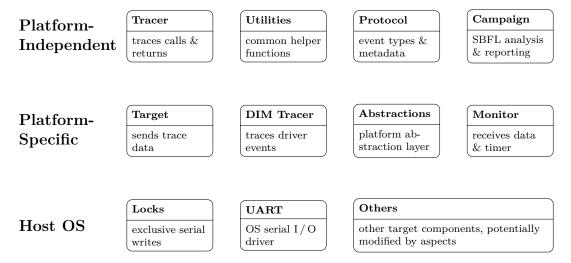

|   | 5.2  | Framework Architecture            | 28 |

|   | 5.3  | Communication Protocol            | 35 |

|   | 5.4  | Data Structures                   | 36 |

| 6 | Den  | oloyment on CyPhOS                | 41 |

|   | •    | Host Platform                     | 41 |

| ii |

|----|

|    |

|     | 6.2<br>6.3<br>6.4 | CyPhOS-Specific Oracles and Transaction Detectors | 44<br>45<br>46 |

|-----|-------------------|---------------------------------------------------|----------------|

| 7   | Eval              | uation                                            | 49             |

|     | 7.1               | Informal Observations on DIMs                     | 49             |

|     | 7.2               | Basic Concepts                                    | 50             |

|     | 7.3               | Fault Synthesis                                   | 51             |

|     | 7.4               | Experiments                                       | 53             |

|     | 7.5               | Memory Requirements                               | 59             |

|     | 7.6               | Threats to Validity                               | 60             |

| 8   | Rela              | ted Work                                          | 63             |

|     | 8.1               | Model-based Diagnosis                             | 63             |

|     | 8.2               | Optimal Suspiciousness Metrics                    | 64             |

|     | 8.3               | Fault Localization in Embedded Devices            | 64             |

|     | 8.4               | Energy Consumption Models                         | 65             |

|     | 8.5               | Learning Cache Replacement Policies               | 65             |

| 9   | Con               | clusion                                           | 67             |

|     | 9.1               | Results                                           | 67             |

|     | 9.2               | Future Work                                       | 68             |

| Gl  | ossar             | y                                                 | 71             |

| Ac  | ronyı             | ms                                                | 75             |

| Bil | oliogi            | raphy                                             | 77             |

| Αp  | pend              | lix                                               | 85             |

| Lis | t of              | Figures                                           | 93             |

| Lis | t of              | Listings                                          | 95             |

| Lis | t of              | Tables                                            | 97             |

| Eid | lesst             | attliche Versicherung                             | 99             |

## Chapter 1

## Introduction

Since the first program was written, bugs have been a steady companion to software developers. In her notes accompanying a 1842 translation of Menabrea's paper on the subject, Ada, Countess of Lovelace, famously proposed a set of computations that could be run by Charles Babbage's analytical engine, a mechanical, Turing-complete computer that only existed as a set of sketches [Men42]. Since her work predates the first operational computer by about a century, she is regarded as the first computer programmer.

In her Note G, a program to compute Bernoulli numbers is described. The program is reproduced in Figure 1.1. In the "Statement of Results" column, it can be seen that step 4 is supposed to compute  $\frac{2n-1}{2n+1}$ . However, the operation in the third column interchanges the source registers, accidentally computing  $\frac{2n+1}{2n-1}$ .

After computers came into widespread use, a plethora of approaches to avoid the introduction of bugs or reduce their severity were tried, but either fell short of their goal or have not yet gained widespread adoption. In the meantime, an immense corpus of software has been developed that most certainly *does* contain bugs. Newer software builds on older solutions, relying on their correctness. This amplifies the impact of bugs in these foundations.

While the idea of rewriting all legacy software, "doing it right this time", might be appealing to debug-weary software developers and users worrying about the safety of their data, it is most definitely not feasible. However, it might be possible to reduce the amount of bugs in existing software to achieve the same goal.

Techniques to identify and eliminate bugs already exist. Commonly, debuggers are used during the development of software to observe the execution of programs, attempting to discover bugs in the process. The discovery of bugs during production use is often aided by the creation of log files that might reveal both an error and its cause during later analysis.

Unfortunately, these approaches consume scarce developer time. A human either has to operate a debugger or interpret log files, and then delve into source code to

Introduction 2

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                    | 1                                                                                                                                                                                                                                                                                                 |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Data. | 1     |                      |               |                         |                          |   |                     | v | Vorking Variables.                                                                                |                              |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Result V       | ariables. |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------------------|---------------|-------------------------|--------------------------|---|---------------------|---|---------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------|------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $ \begin{vmatrix} - & v_1 & v_1 & v_2 & v_3 & v_4 & v_4 & v_5 & v_5 & v_5 & v_6 & v_6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Nature of Operation. | acted                                                                                                                                                                                                                                                                                             | receiving                                                                            | change in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Statement of Results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0 0 1 | 0 0 2 | 0 0 4 | 0                    | 0             | 0                       | 0                        | 0 | 0                   | 0 | 0                                                                                                 | 0                            | 0                                                                              | B <sub>1</sub> in a<br>decimal C<br>fraction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |           | 0000 |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -<br>+<br>+<br>-     | $V_4 = V_5$ $V_5 + V_6$ $V_6 + V_7$ $V_{11} \leftarrow V_{12}$ $V_{12} \leftarrow V_{13}$                                                                                                                                                                                                         | 2V <sub>4</sub>                                                                      | $\begin{cases} 1V_1 = 1V_1 \\ 1V_8 = 2V_5 \\ 1V_1 = 1V_1 \\ 2V_5 = 0V_5 \\ 2V_4 = 0V_4 \\ 1V_2 = 1V_2 \\ 2V_{11} = 0V_{11} \\ 1V_2 = 1V_2 \\ 2V_{11} = 0V_{11} \\ 1V_{12} = 1V_{12} \\ 1V_{13} = 1V_{14} \\ 1V_{14} = 1V_{15} \\ 1V_{15} = 1V_{15} \\ 1V_{$ | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 1   | <br>2 |       | 2 n - 1<br><br>0<br> | 2n+1<br>0<br> |                         |                          |   |                     |   | $\frac{\frac{2n+1}{1}}{\frac{1}{2} \cdot \frac{2n-1}{2n+1}}$                                      |                              | $-\frac{1}{2}\cdot\frac{2n-1}{2n+1}=\Lambda_{\phi}$                            | White distribution of the state |                |           |      |

| $ \begin{vmatrix} + v_1+v_2  v_3 & - v_1  & - v_2  & - v_3  \\ + v_0+v_2  v_3 & - v_2  & - v_3  & - v_3  \\ + v_0+v_2  v_3 & - v_2  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  & - v_3  & - v_3  \\ + v_1+v_2  v_3 & - v_3  & - v_3  $ | $ \begin{vmatrix} + v_1+v_2  v_2 & & & & & & & & & & & & & & & & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ÷<br>×<br>+          | 1V <sub>6</sub> ÷ 1V<br>1V <sub>21</sub> ×3V<br>1V <sub>12</sub> +1V                                                                                                                                                                                                                              | 7   3V <sub>11</sub><br>11   1V <sub>12</sub><br>13   2V <sub>13</sub>               | $\begin{bmatrix} v_{11} = v_{11} \\ v_{21} = v_{21} \\ v_{11} = v_{11} \end{bmatrix}$<br>$\begin{bmatrix} v_{12} = v_{12} \\ v_{11} = v_{12} \end{bmatrix}$<br>$\begin{bmatrix} v_{12} = v_{12} \\ v_{12} = v_{12} \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |       |       |                      |               | 2 n                     | 2                        |   |                     |   | $\frac{2n}{2} - \Lambda_1$                                                                        | $B_1, \frac{1}{2} = B_1 A_1$ | $\left\{-\frac{1}{2} \cdot \frac{2n-1}{2n+1} + B_1 \cdot \frac{2n}{2}\right\}$ | В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $ \begin{bmatrix} \left\{ \times v_{y} \times v_{11} v_{12} \dots \left\{ v_{11} - v_{12} - v_{12} \right\} - \frac{s^{2} - 2}{2} - \frac{s^{2} - 1}{3} - \frac{s^{2} - 2}{4} - \lambda_{3} & \cdots & \cdots & \cdots & 0 \\ \left\{ \times v_{12} \times v_{11} v_{12} \dots \left\{ v_{11} - v_{12} - v_{12} \right\} - \frac{s^{2} - 2}{2} - \frac{s^{2} - 2}{3} - $ |                      | + 1V <sub>3</sub> + 1V <sub>4</sub> - 2V <sub>6</sub> + 2V <sub>8</sub> - 2V <sub>6</sub> - 1V <sub>8</sub> - 2V <sub>6</sub> - 1V <sub>1</sub> + 1V <sub>1</sub> + 2V <sub>1</sub> - 3V <sub>6</sub> + 3V <sub>1</sub> × 1V <sub>8</sub> × 5V <sub>1</sub> + 2V <sub>10</sub> + 2V <sub>10</sub> | 7 2V7 7 3V8 7 3V8 7 1 4V11 7 1 5V6 7 1 7 2V7 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | $\begin{cases} V_1 = V_1 \\ V_2 = 2V_2 \\ 2V_6 = 2V_6 \\ 2V_7 = 2V_7 \\ 2V_7 = 2V_7 \end{cases}$ $\begin{cases} V_8 = 9V_8 \\ 2V_1 = 2V_1 \\ 2V_1 = 1V_1 \end{cases}$ $\begin{cases} V_8 = 3V_6 \\ 1V_1 = 1V_1 \\ 1V_2 = 2V_2 \\ 2V_2 = 2V_2 \end{cases}$ $\begin{cases} V_8 = 2V_6 \\ 2V_7 = 2V_7 \\ 2V_1 = 2V_1 \\ 2V_1 = 2V_1 \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $ \begin{array}{c} = 2 + 1 - 3 \\ = 2 m - 1 \\ = 2 m - 1 \\ = 2 u - 2 \\ = 3 u - 1 \\ = 2 u - 2 \\ = 3 + 1 = 4 \\ = 2 u - 2 \\ = 3 + 1 = 4 \\ = 2 u - 2 \\ = 3 - 2 \\ = 2 u - 2 \\ = 3 u $ | 1     |       |       |                      |               | 2 n - 1 2 n - 1 2 n - 5 | 3<br>3<br><br>4<br>4<br> |   | 2 n -<br>4<br>0<br> | 2 | $\begin{cases} \frac{2n}{2} \cdot \frac{2n-1}{3} \cdot \frac{2n-2}{3} \\ = \lambda_3 \end{cases}$ | Вз Аз                        | 1.                                                                             | }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | В <sub>3</sub> |           |      |

Figure 1.1: Ada, Countess of Lovelace's program to compute Bernoulli numbers<sup>1</sup>

locate a bug. Additional roadblocks to debugging might be hard-to-read legacy code, unusual coding conventions and lack of architectural knowledge.

Even without these obstacles, finding the bug is hardly guaranteed. A log file might omit relevant information due to storage constraints. If the bug only occurs in a specific environment, e.g., due to being triggered by a specific combination of input data, debugging can only be performed in a faithful emulation of this setting. Infrequently triggering bugs would require debugging sessions over a time span of hours or even days. In the worst case, the presence of a debugger or detailed logging might even suppress the bug.

Such hurdles to debugging and logging are more common in low-level software, e.g., operating systems and software running on embedded devices, although they are hardly exclusive to it. However, most approaches suited to embedded systems can scale up to more forgiving environments.

This thesis presents a different approach to localizing bugs that can meet those challenges. By automating monitoring of a system over long periods and automatically suggesting likely causes of a bug, manual work can be reduced and developer time saved.

<sup>&</sup>lt;sup>1</sup>Digitization from The Erwin Tomash Library On The History Of Computing, https://www.computer.org/cms/Tomash catalog web/index.htm.

3 Objectives

### 1.1 Objectives

A framework for the localization of bugs that implemented this approache was developed for this thesis. It is capable of monitoring a system during its run time, collecting information about it and creating a report from the processed data that can be displayed to a human developer. To guide implementation and development, four major objectives were defined, outlining the requirements the framework must satisfy.

The first requirement is that the framework should assist in the localization of bugs. By providing accurate suggestions on locations in a program's source code where a bug might originate, developers can focus their efforts on these locations, skipping unrelated components. This objective was achieved using spectrum-based fault localization. Some extensions to the process are investigated for the thesis.

Classic spectrum-based fault localization is not suited to localize bugs in long-running system due to requiring occasional manual intervention. To save valuable developer time, analysis should instead be performed **autonomous**ly over an extended time period; human labor should only be required to analyze the results, not gather them. Autonomy was achieved using generic analysis components, oracles and transaction detectors, that were created using machine learning.

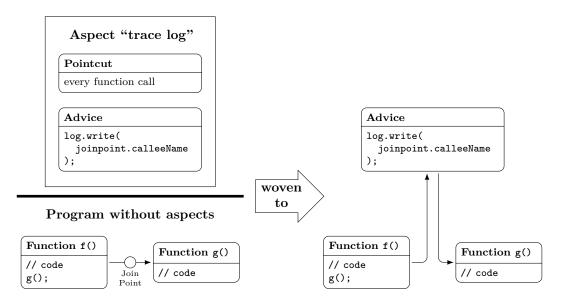

Since the framework explicitly targets existing and even legacy software, the analysis framework must be **retrofittable** into preexisting software with little effort. Ideally, the software under examination should require no modification, in practice, small and localized changes might be unavoidable. Since certain bugs might be obscured by invasive diagnostics, this gathering of information must be as **non-intrusive** as possible. This requirement was satisified using aspect-oriented programming techniques.

In privileged operating system code, a bug can easily corrupt unrelated data or require a hardware reset to restore functionality. To facilitate analysis of such bugs, the analyzing system must **operate in isolation** from the diagnosed system to maintain integrity of the stored information. Since this isolation can not be guaranteed on the same system, **physical isolation** – separation of examined and analyzing system – was necessary.

#### 1.2 Contributions

Three novel contributions to the state of the art are presented in this thesis:

1. The extensions to spectrum-based fault localization, with the exception of method call sequence hit spectra, have not previously been discussed.

Introduction 4

2. The use of generic, machine-learned oracles and transaction detectors is a new approach. The driver interaction models used as generic oracles are a novel method for modeling the communications between a driver and the managed periphery.

3. An autonomously operating fault localization framework using embedded devices has not yet been investigated; past approaches were limited to fault localization with major human involvement.

#### 1.3 Structure of this Work

This thesis is structured into nine chapters. Chapter 2 describes the use of spectrum-based fault localization to pinpoint bugs. These ideas are extended to long-running systems in Chapter 3. Chapter 4 then outlines how analysis data can be acquired using aspect-oriented programming.

These foundations having been laid, Chapter 5 describes the implementation of the analysis framework using these concepts; Chapter 6 then outlines the integration into the operating system CyPhOS and the issues encountered.

Chapter 7 details the experiments used to evaluate the work and outlines the results, followed by a discussion on related work that was not adapted for this thesis in Chapter 8. Finally, in Chapter 9, conclusions from these results are drawn and an outlook on future work is given.

## Chapter 2

# **Spectrum-Based Fault Localization**

This chapter discusses the use of spectrum-based fault localization to the localize bugs. First, a standard terminology to formalize the notion of "bugs" will be introduced, then, the fundamentals of spectrum-based fault localization and how it was applied in the scope of this thesis are described. Finally, three extensions to the process are presented.

### 2.1 Standard Terminology for Defects

Avižienis et al. provide a standard terminology to formally describe "buggy software". Using this terminology, a **system** [Avi+04] is an entity (e.g., a program) that interacts with other entities. These other entities might be other systems, human users, hardware etc. A system can often be broken up into smaller systems, **components** [Avi+04].

The intended operation, including functionality, performance, etc., of a system is called its **function** [Avi+04]. In contrast to this, a system's **behavior** [Avi+04] is its actual operation, i.e., the implementation of the desired function. The part of the behavior that can be perceived by a system's users is called **service** [Avi+04].

As an example, assume that an array-backed list class for use in a collection library is being implemented. In this case:

- the system is the list implementation,

- the list's function comprises the *intended* semantics of the list's operations, e.g., adding and removing of elements, but also the storage implementation hidden from a user,

- the list's behavior comprises the semantics "as programmed", including the implementation of its operations, but also routines for on-demand storage enlargement, and

• the service comprises the semantics "as programmed", except for the internal state.

Having formalized a concept of "software" and its intended operation, the notion of "bugs" can be replaced by more precise terms separating cause and effect. A **failure** [Avi+04] occurs when a system's service deviates from the service intended in its function. Meanwhile, a **fault** [Avi+04] is the cause of a failure. **Fault localization** [Avi+04] attempts to pinpoint the root cause of an observed failure, i.e., find the underlying fault.

To continue the previous example, assume that the list implementation erroneously ignores removal operations. Then,

- the fault is located in the code that is supposed to handle removals, but

- the failure only manifests when a client recovers an element from the list that had previously been deleted, and

- fault localization would then try to locate a function or even line of code in the removal code that causes this failure.

While this terminology is applicable to a many types of system, this thesis concentrates on **programs** that can be separated into components such as modules, functions, lines of code or statements.

For added clarity, a program's execution will be referred to as a **run** and the program as **running**. A run begins with the program's start and ends with its termination, if at all. The term **execution** shall be reserved for components. During a program's run, some or all of its components are **executed** one or more times.

If a program's run is recorded, the chronological sequence of all component's executions<sup>1</sup> is called the run's **trace** [DLZ05]. A trace of the sequential executions of the components A, B and C is written as

$$\langle A, B, C \rangle$$

.

As an additional convention, if a failure is observed during a program's run, this run is called **failing**, otherwise **succeeding**. These terms also apply to a corresponding trace. Components that contain a fault are called **faulty**.

This terminology allows for a precise description of a "bug", its cause, effect and location.

<sup>&</sup>lt;sup>1</sup>Considerations for multi-threaded programs will be discussed in Section 2.6.

7 Basic Concepts

#### 2.2 Basic Concepts

Spectrum-based fault localization (SBFL) exploits the fact that if a failure was observed during a program's run, at least one faulty component must have been executed and must therefore be present in the run's trace.

A single trace only permits the conclusion that components that were not executed can not have contributed to the failure. The combination of data from multiple failing and succeeding runs allows to pinpoint the faulty component further. SBFL assumes that, when examining a set of traces, the execution of a faulty component is correlated with the observation of a failure.

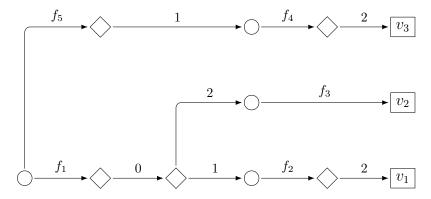

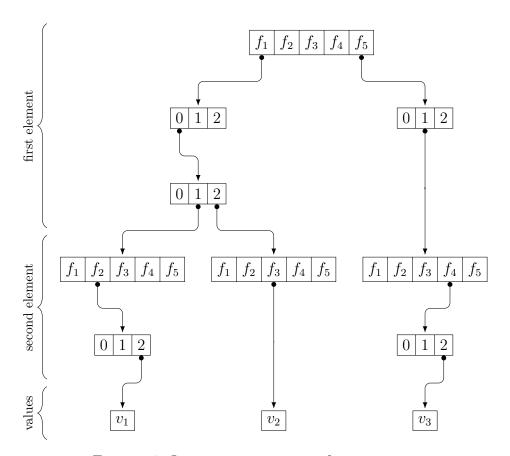

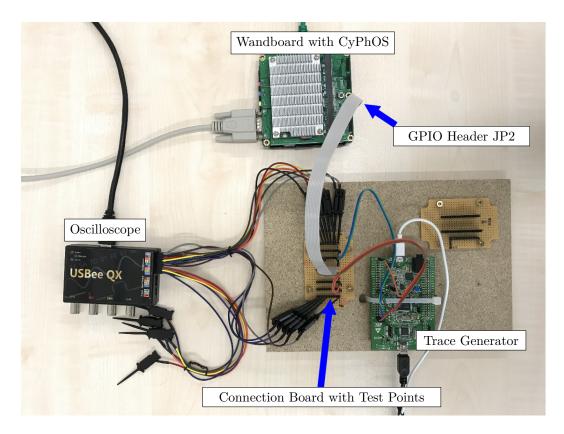

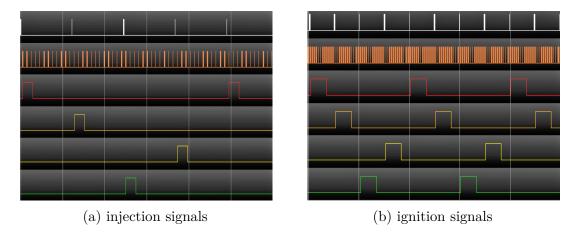

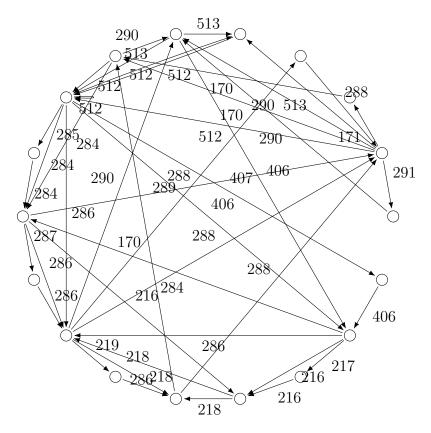

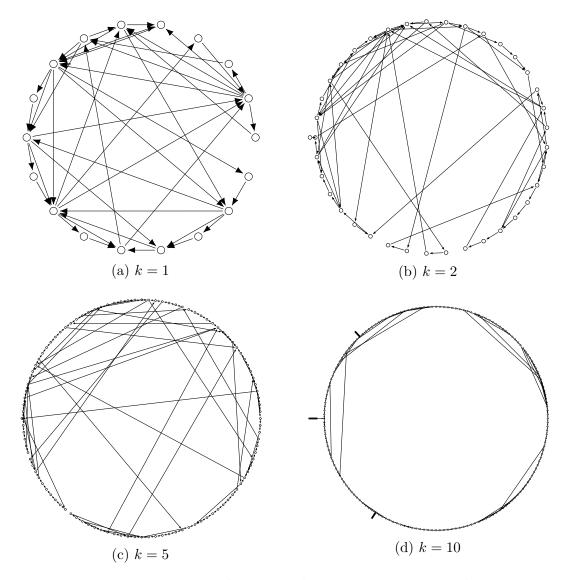

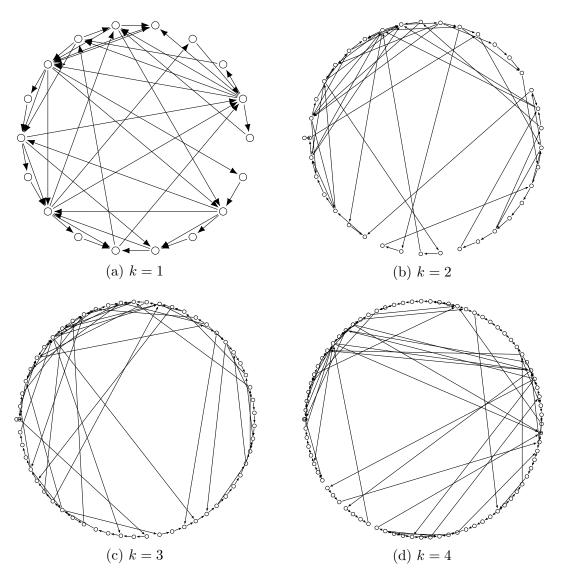

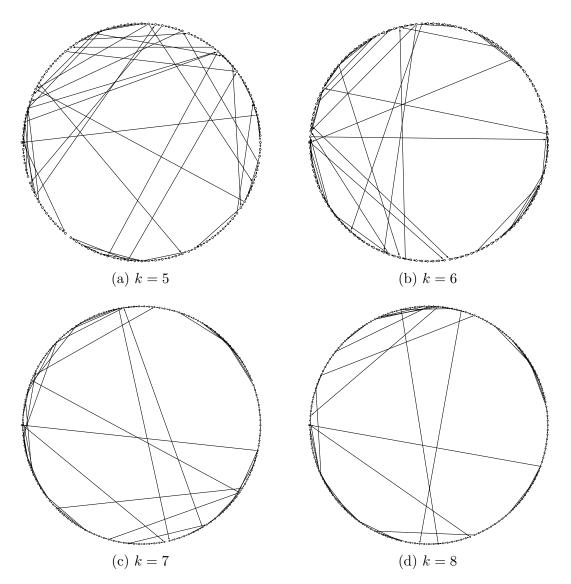

To study this correlation, the components executed during a run need to be recorded. Given a program separated into k components  $C_0, \ldots, C_{k-1}$  that was run a single time, a vector  $S \in \{0, 1\}^k$